加入clockpad后仿真发现延时太大了

时间:10-02

整理:3721RD

点击:

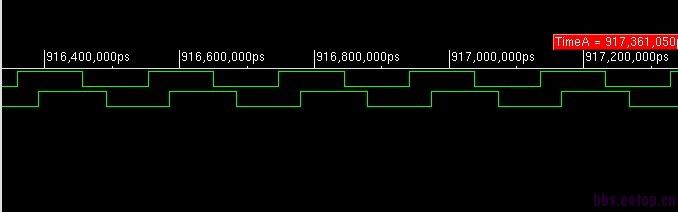

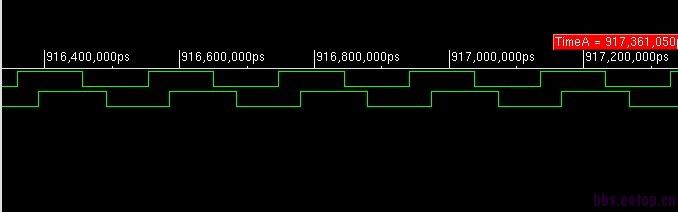

今天用.35的工艺库加入了clock pad,用DC综合后产生sdf文件和网表。但是用ncverilog仿真时发现输入时钟和输出时钟延时有点大(20多ns),我的时钟也就190多ns。看了看timereport发现没有violation。延时过大这个现象正常吗?还是我的操作有问题? 求大神指点迷津!这是我的截图,上面是输入时钟下面是输出时钟:

补充一下,我添加的时钟pad是pc3c01,1x的驱动能力。用的库是chrt35的库,求各位帮帮忙啊!