请问encounter如何加VDD/VSS的IOpad和连线

时间:10-02

整理:3721RD

点击:

我的verilog netlist 里面根本没有 VDD 和 VSS 这两个端口和信号。

只是在 .io 文件里加了两句

Pad: VDD W PAVDD

Pad: VSS W PAVSS

于是在生成的 layout 上的确出现了 VDD 和 VSS 这两个 pad。 但是发现没有任何从Core伸出的与 VDD/VSS 连接的连线。

其他的IO都能看到细细的连出线。

我也试着在power-> connect global net 里面设置的一些东西,结果VDD 和 VSS 这两个 pad 仍然什么都没有连。

请问大侠,是不是有哪些关键步骤让我给漏掉了?

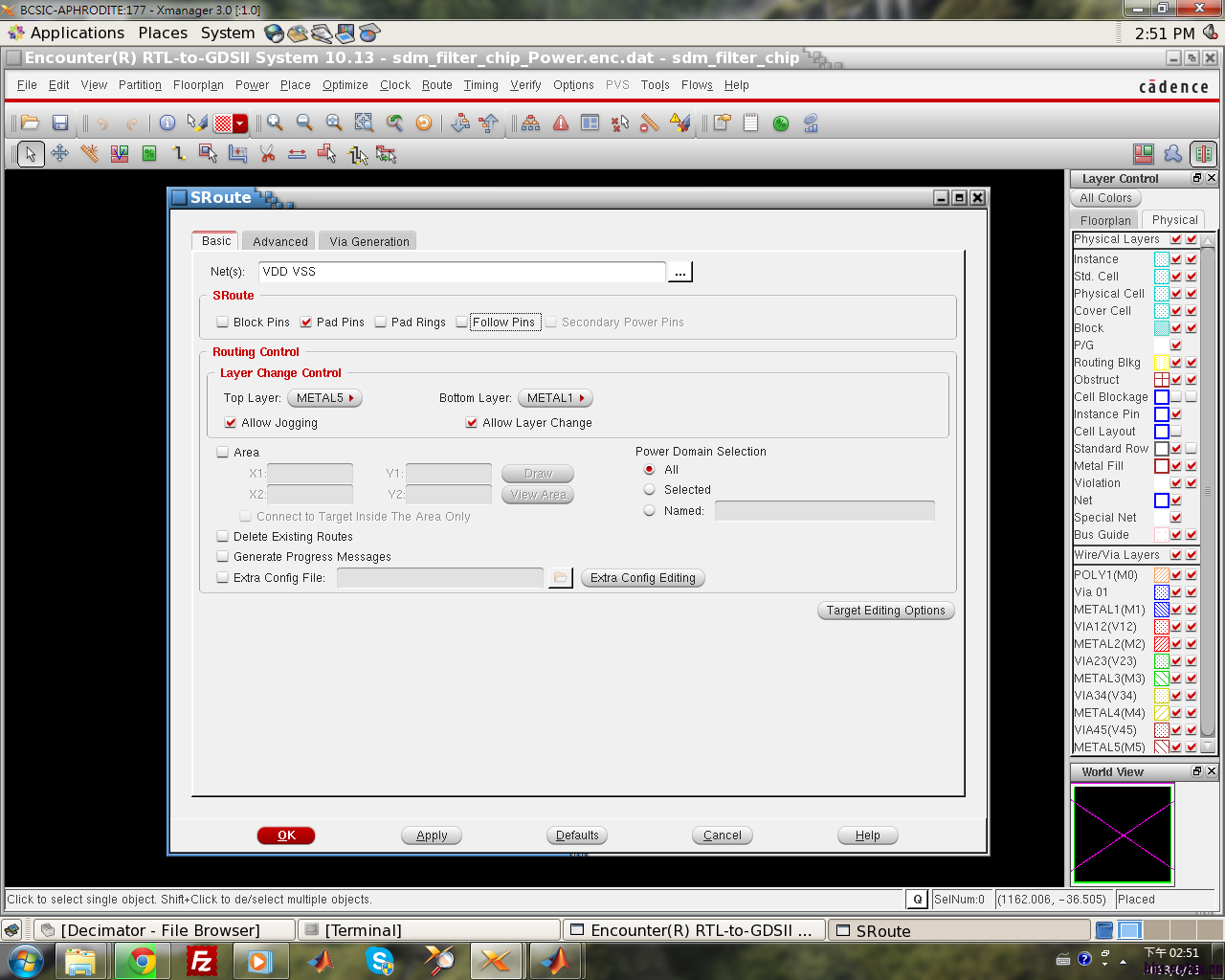

而Global Net Connection只是定义power的称而已,定义了以后才可在上图的Net(s)中找到它的名称

只是在 .io 文件里加了两句

Pad: VDD W PAVDD

Pad: VSS W PAVSS

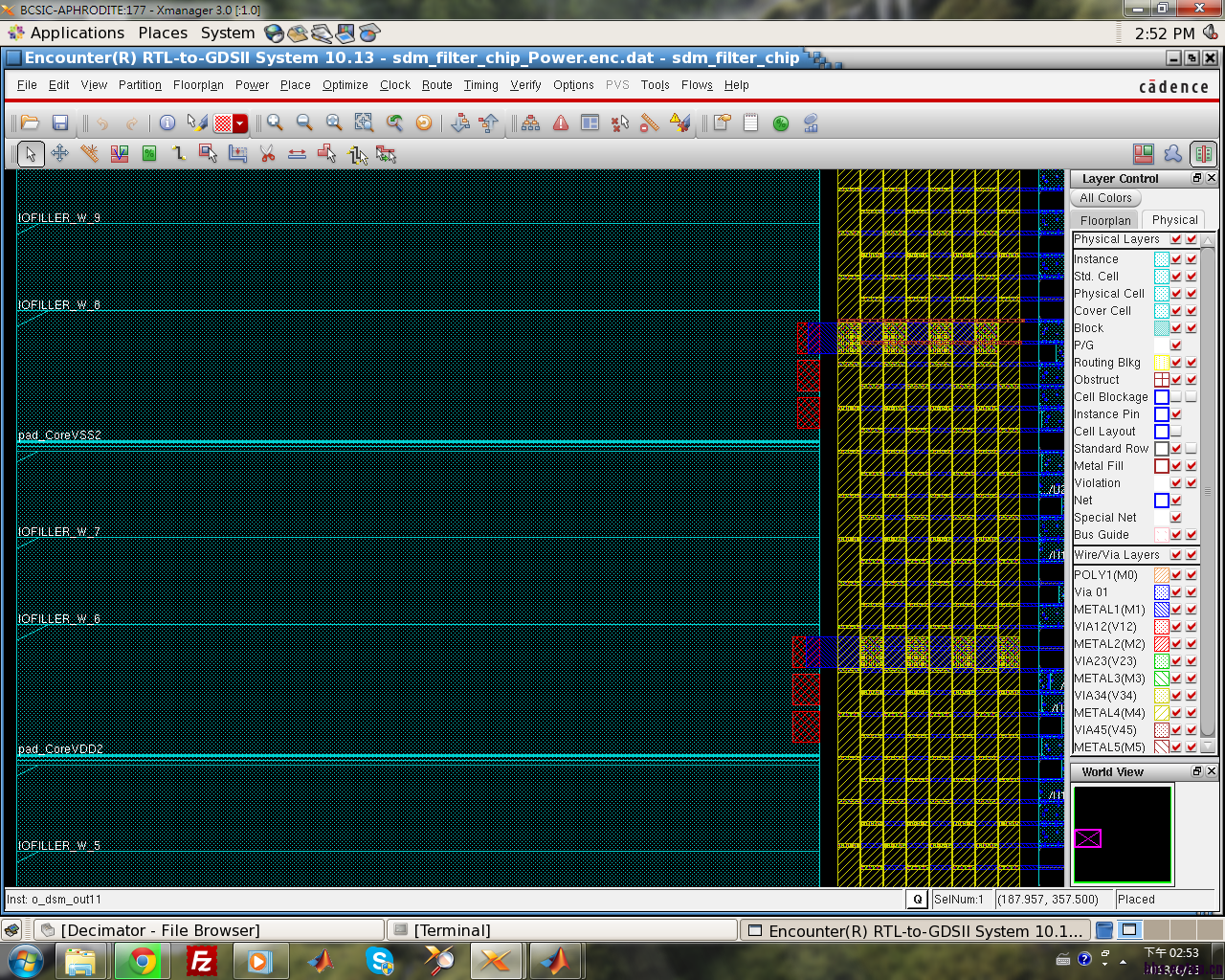

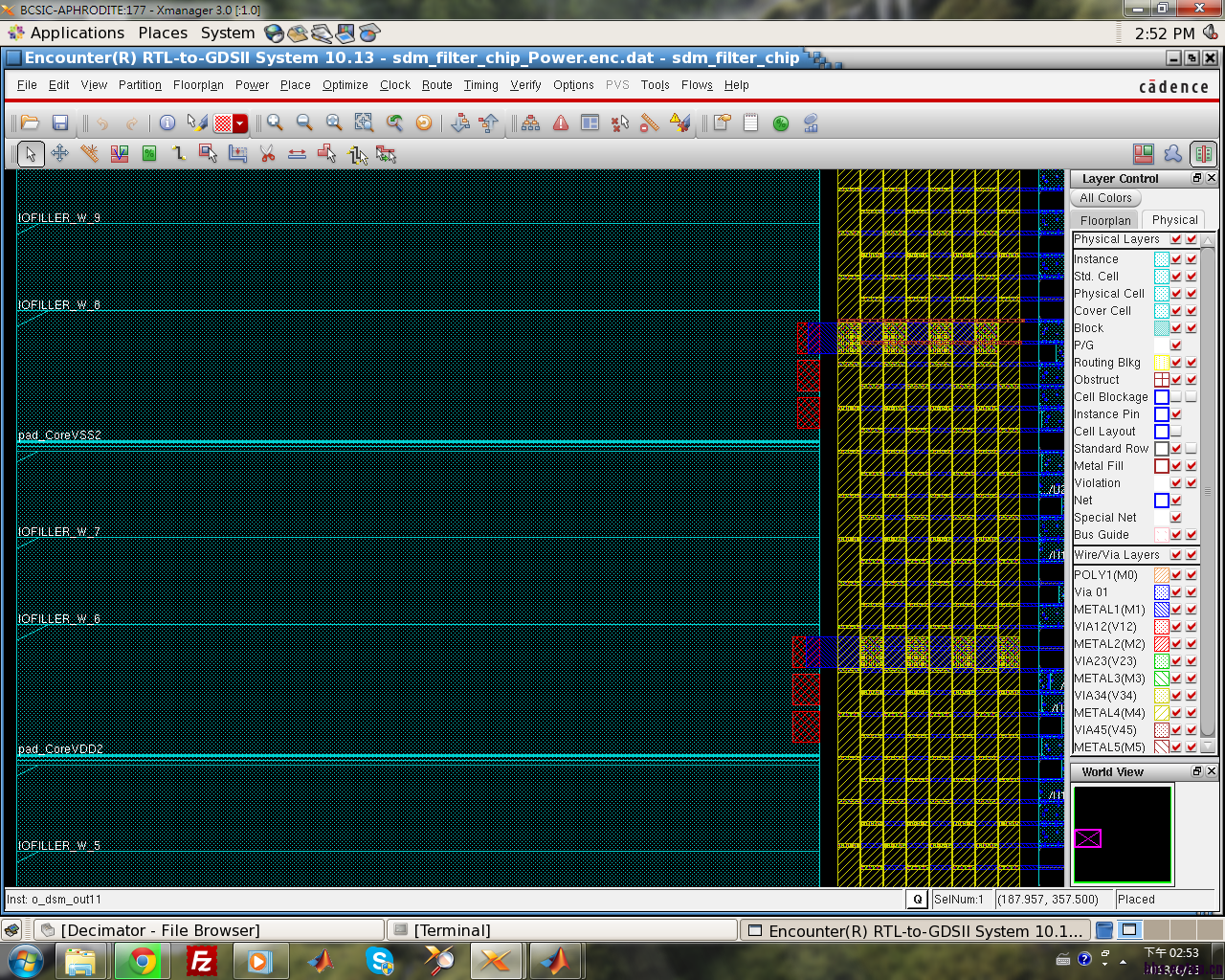

于是在生成的 layout 上的确出现了 VDD 和 VSS 这两个 pad。 但是发现没有任何从Core伸出的与 VDD/VSS 连接的连线。

其他的IO都能看到细细的连出线。

我也试着在power-> connect global net 里面设置的一些东西,结果VDD 和 VSS 这两个 pad 仍然什么都没有连。

请问大侠,是不是有哪些关键步骤让我给漏掉了?

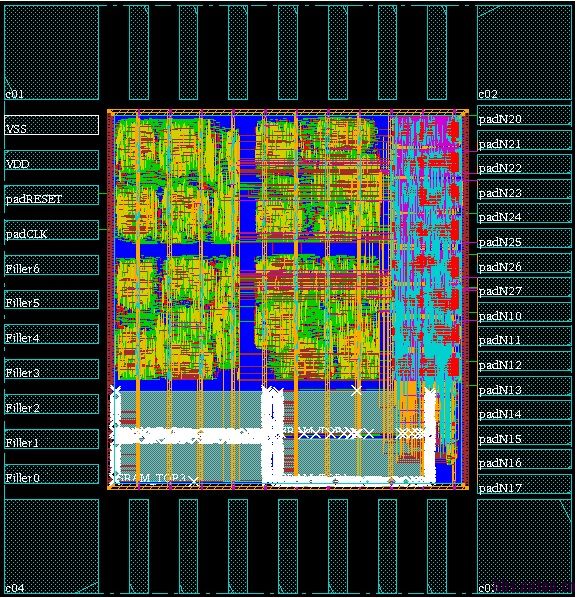

发现VDD 和VSS 可以用 saveNetlist -includePowerGround myDesign.v 这个命令,生成新的Verilog文件。发现这回门级的器件里都出现了VDD 和VSS两个端口。但是顶层的模块和之前没有什么变化。

虽然,对我来说,已经更近一步了。但是用encounter生成版图的时候,发现VSS和VDD的pad仍然没有和core相连。

我怀疑是Global Net Connect 没有用对。请高手指点。

如下图所示:(VDD 和 VSS两个pad 没有连线)

你还要点Route -> Special Route,然后在Net(s)里填入VDD和VSS,接着在SRoute那栏里只勾选Pad Pins然后OK就行了

而Global Net Connection只是定义power的称而已,定义了以后才可在上图的Net(s)中找到它的名称

多谢大侠。我学习一下了。

我也出现了这样的问题,但在SRoute那栏里只勾选Pad Pins,还是不行啊!

也可以自己画,wire edit

学习试试~

learning !

IO 上的VDD VSS与core的电源的连接我个人还是喜欢手动去连接的。