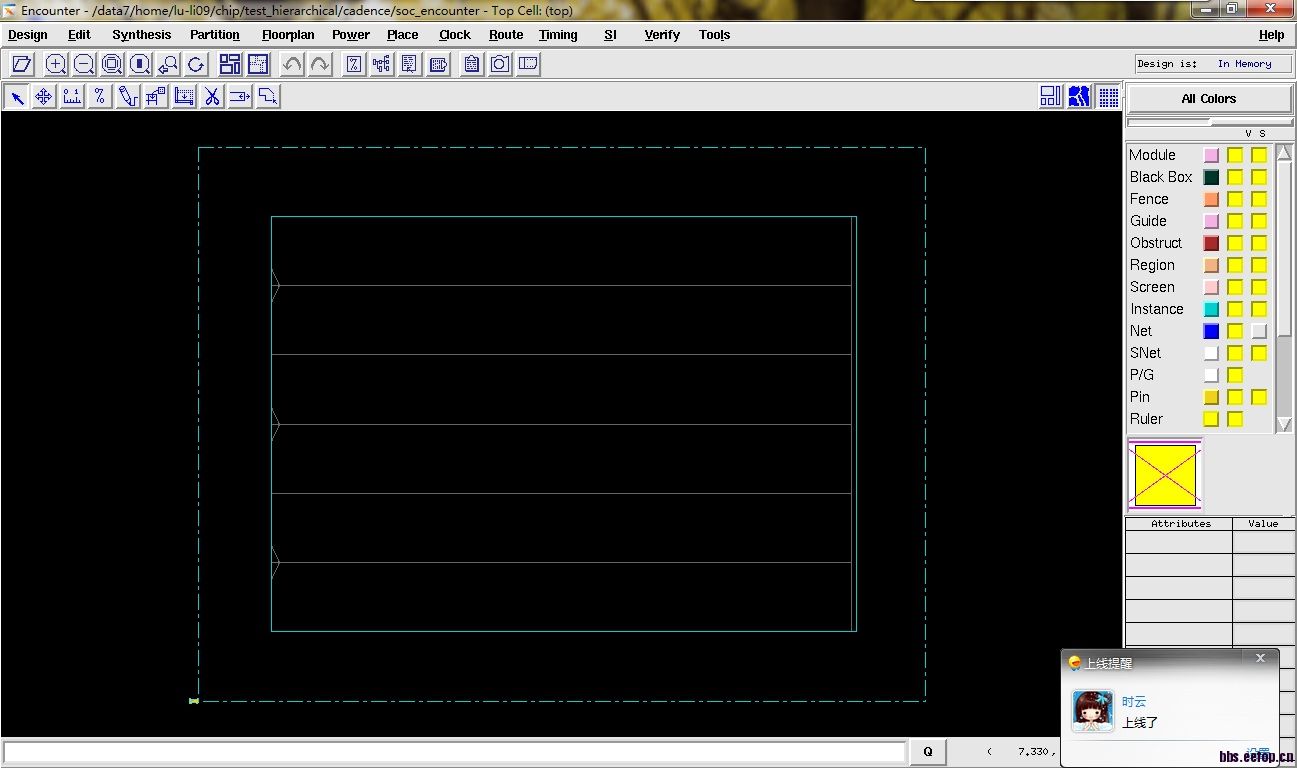

soc encounter 如何对设计分区

谢谢

选中module按Q键

修正Attribute,Constraint Type改为Fence

您好,谢谢您的解答,不过我导入顶层的网单时,并没有看到有module的信息和视图,请问在什么位置,还有导入netlist时,encounter是否自己会识别module?谢谢

是不是没在floorplan mode 下按钮在ALL color左边

谢谢,不过在floorplan 视图下也没有?但,我往下做,是可以的,能够放cell,就是看不到module,

下面是我的顶层网单

module counter2 ( clk, rst, din, dout2 );

output [3:0] dout2;

input clk, rst, din;

wiren1, n2, n3, n4, n5, n6, n7, n8, n9;

MXI2X1 U6 ( .A(dout2[1]), .B(n1), .S0(n2), .Y(n7) );

NAND2X1 U9 ( .A(dout2[2]), .B(n3), .Y(n4) );

OAI2BB2X1 U10 ( .B0(n4), .B1(dout2[3]), .A0N(n4), .A1N(dout2[3]), .Y(n5) );

INVX2 U11 ( .A(rst), .Y(n8) );

XOR2X1 U8 ( .A(n3), .B(dout2[2]), .Y(n6) );

DFFRX2 \dout2_reg[1]( .D(n7), .CK(clk), .RN(n8), .Q(dout2[1]), .QN(n1) );

DFFRX2 \dout2_reg[0]( .D(n9), .CK(clk), .RN(n8), .Q(dout2[0]) );

DFFRX2 \dout2_reg[2]( .D(n6), .CK(clk), .RN(n8), .Q(dout2[2]) );

DFFRX2 \dout2_reg[3]( .D(n5), .CK(clk), .RN(n8), .Q(dout2[3]) );

NOR2X1 U3 ( .A(n2), .B(n1), .Y(n3) );

NAND2X1 U4 ( .A(din), .B(dout2[0]), .Y(n2) );

XOR2X1 U5 ( .A(din), .B(dout2[0]), .Y(n9) );

endmodule

module counter1 ( clk, rst, dout1 );

output [3:0] dout1;

input clk, rst;

wireN2, N3, N4, n1, n3, n4, n5, n6, n7;

INVX2 U3 ( .A(rst), .Y(n1) );

MXI2X1 U9 ( .A(n3), .B(dout1[0]), .S0(dout1[1]), .Y(N2) );

JKFFSX2 \dout1_reg[0]( .J(1'b1), .K(1'b1), .CK(clk), .SN(n1), .Q(n3), .QN(

dout1[0]) );

DFFRX2 \dout1_reg[2]( .D(N3), .CK(clk), .RN(n1), .Q(dout1[2]) );

DFFRX2 \dout1_reg[1]( .D(N2), .CK(clk), .RN(n1), .Q(dout1[1]) );

DFFRX2 \dout1_reg[3]( .D(N4), .CK(clk), .RN(n1), .Q(dout1[3]) );

NAND3X1 U5 ( .A(dout1[1]), .B(dout1[2]), .C(dout1[0]), .Y(n4) );

NAND2X1 U6 ( .A(n4), .B(dout1[3]), .Y(n5) );

OAI21X1 U7 ( .A0(n4), .A1(dout1[3]), .B0(n5), .Y(N4) );

NAND2X1 U8 ( .A(dout1[0]), .B(dout1[1]), .Y(n6) );

NAND2X1 U10 ( .A(n6), .B(dout1[2]), .Y(n7) );

OAI21X1 U11 ( .A0(n6), .A1(dout1[2]), .B0(n7), .Y(N3) );

endmodule

module top ( clk, rst, dout1, dout2 );

output [3:0] dout1;

output [3:0] dout2;

input clk, rst;

counter1 u1 ( .clk(clk), .rst(rst), .dout1(dout1) );

counter2 u2 ( .clk(clk), .rst(rst), .din(dout1[3]), .dout2(dout2) );

endmodule

你的单元太少了的缘故

我不知道你的encounter的版本

在91里面是Options--Set Preferences---Display---找到Min. Floorplan Module Size: num

默认是100,你自己改成10,Apply一下,再看看。

非常感谢您的解答,问题已经解决!

小编用的什么版本的encounter啊,好像在win7下用的

他用的是vritosou

学习了

认真学习中……

谢谢,受益了

学习了

请问下,是怎么解决的,我的是8.1版本的,如果你是9.1版本,并按小编说的方法改正确了,能否说一下命令

thanks

学习啦,谢谢

找了几天,终于找到答案