rtl阶段读取saif文件的反标百分比问题

前端用rtl做了一个simulation,得到vcd file之后转化成为rtl_saif文件,给dc做综合

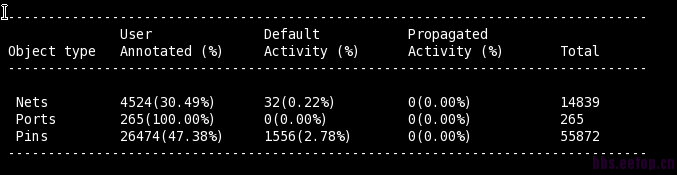

dc综合时读取rtl文件,并且读取这个rtl_saif文件。但是在report_saif之后发现部分net和pin没有被反标上。

tcl如下:

read_saif -input rtl_saif -instance $core_path -rtl_direct

report_saif

请问,这个脚本的流程有哪里信息缺失导致saif不能100%反标么?补充一下,我们试过将dc出来的netlist去做gate level的仿真,并且得到gate_saif,用gate_saif和dc_netlist给dc做第二次综合,那么这些saif信息就能100%的反标上。

不知道 saif 的格式是怎样,可能有点想当然:DC 出来之后会多出一些 net,也有一些 net name 跟 rtl 是不一样的;另外为什么不做 gate level 的 saif 而要做 rtl 的仿真,你不能说 DC 的优化程度对 toggle rate 没有影响啊。

gate_level的saif file之前做了。而且这个才是标准的流程吧?

rtl出来的这个saif,是想对比一下和gate_level的saif对power的不同优化。

看到一份台湾的关于功率优化的资料,里面有下面这样的描述,说是只有边界的switch信息才被记录,并非所有点都记录,因此达不到100%的反标。

“RTL Power Optimization顧名思義就是藉由RTL simulation來獲得hierarchy boundary及

registers這些點的switch activity資訊。Power Compiler便可依此資訊做Power Optimization。

但合成前所獲得之switch activity資訊僅限於boundary而並非所有點,因此該流程一般是作為

功率評估之用”

看到一份台湾的关于功率优化的资料,里面有下面这样的描述,说是只有边界的switch信息才被记录,并非所有点都记录,因此达不到100%的反标。

“RTL Power Optimization顧名思義就是藉由RTL simulation來獲得hierarchy boundary及

registers這些點的switch activity資訊。Power Compiler便可依此資訊做Power Optimization。

但合成前所獲得之switch activity資訊僅限於boundary而並非所有點,因此該流程一般是作為

功率評估之用”

对的,我也这么认为!

DC阶段读入saif文件可以优化功耗?