解决tran的问题

就是在中间插buffer啊,加的buffer驱动够就行

您好,在中间插,会不会影响其他path的timing,只是单纯在中间插就行吗?我应该怎么来排查,多谢

如果timing不是特别紧的话,直接上高级货。add_buffer_on_route 轻松解决长线的问题。

那条命令很强大,其实我纠结的是,假如我想在长net上的A点插buffer,那我需要report一下这个A点前面的timing?还是后面的?需要看slack?还是不需要分析?感觉自己不会分析,可以指导下吗?通过什么命令来分析A点是否可以插,不会对其他path造成影响

插入之后用report_timing -through A报一下setup/hold不就可以吗

插入buffer后在pt里报一下最好的corner下hold经过A点的路径是否存在违例,没有的话就行。

谢谢您的回复,其实我纠结的是,在实际操作时,我应该先分析哪些东西,来决定A点这个地方是否可以插buffer?因为我怕直接插会影响到其他的timing path,但是又不知道改怎么提前分析?

很高兴收到您的回复,我其实是想知道在插buffer之前,应该怎么去分析分析,找到一个合适的A点?怎么提前看是否这里插了0.2ns的buffer,会不会导致其他的path

的timing violation。插之前什么都不需要考虑吗?

你在插buffer之前在PT中报一下这条path的setup hold的余量就可以,一般不会影响hold。对其他path的影响一般都没有,你是在data path上面插buffer,不会动到clock,所以对其他path的影响不大。最多受影响的就是经过这条net前后cell的path。但是可能会有noise的影响,这些你都得插完buffer之后才能看得出来。

可以现在pt中塞buffer,报一下timing看看有没有影响,transition过没过、再回到edi或icc中去塞,这样子比较保险一些。

谢谢您的回复,请问,为什么会有noise,你的意思是插完buffer,增加了这个net上的驱动力,会影响到附近的net?

另外,noise无非就是两条net之间的影响,你在实际工程中遇到noise问题会怎么解决?做些size cell 和插buffer吗?如果noise不是很大,应该也不用修吧?timingOK 就行。noise有经验值吗?一般多大不用管?

楼上正解,其实这类错误一般肯定是解掉的,粗暴点在invs里直接插cell就行,一般来说都不会引起其他vio 问题。至于在pt里怎么插,在哪里插,请查找pt命令。

我看了下PT 的useguide,怎么在PT中的长net插buffer啊?因为PT没有物理信息啊,只显示了一个net的名字。insert_buffer net25 buff ,并不能保证插在了这根长net的中间啊,请前辈指导

pt里看当然不准确了,就是在invs里看tran大小决定插多大buffer&inv,插一级还是几级,完事了去pt里面重新看一下插入点的路径是否违例。tran违例的地方是单一路径基本不影响其他path,要么这条tran违例附带影响很多path,结果会变好,不太可能出现很严重的其他path违例。

您说根据tran的大小决定来插多少和多大驱动的buffer,我想举一个具体的例子:

cellA的输出pin 经过net接到cellB输入pin,在pin上报了-0.2的violation。lib中cellB的输入pin,允许的最大的tran是0.5,也就是实际到达这个pin的tran是0.7,那我应该去找一个buffer来解tran,在lib中看这个buffer的输出pin的什么属性?来看是否这个buffer可以修好?这个问题想了好久好纠结

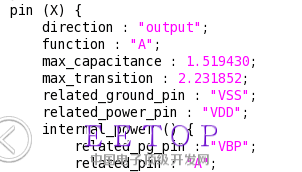

pin (X) {

direction : "output";

function : "A";

max_capacitance : 0.307449;

max_transition : 0.664800;

min_capacitance : 0.000070;

你可以把这条net上的所有path都报出来,或者报一条最差的,然后在这个基础上修改,transition太大的话,先看看经过该net的所有的path有没有hold violation,如果有的话估计插入buffer后hold可能会更严重,(前提是插入的buffer的delay与修复transition减小的delay相比跟小,因为数据速度更快了),如果有setup violation的话,插入buffer的话可能会对setup slack有好处,因为数据速度被加快了,可以看看从库中找个合适的buf。

其实我迷茫的地方时:怎么根据tranviolation的大小决定来插多少和多大驱动的buffer?去库里找buffer,看这个buffer的什么属性?

举一个具体的例子:

cellA的输出pin 经过net接到cellB输入pin,在cellB的pin上报了-0.2的violation。lib中cellB的输入pin,允许的最大的tran是0.5,也就是实际到达这个pin的tran是0.7,那我应该去找一个buffer来解tran,在lib中看这个buffer的输出pin的什么属性?来看是否这个buffer可以修好?

pin (X) {

direction : "output";

function : "A";

max_capacitance : 0.307449;

max_transition : 0.664800;

min_capacitance : 0.000070;

该net自身的cap过大(比如走线过长等)和该net后面接的输入的cap过大,真要确定是什么位置放置buffer,好像也没有什么具体的规定吧,那就朝着减小net上的cap这个方向来决定好了

嗯嗯,您说的对我很有帮助,我其实就是不会看lib,从lib中挑选合适的buffer,

假如出现max tranviolation在一个cell的属兔pin上,我找一个buffer来插,那我看这个buffer的输出pin的什么指标?在实际去lib找buffer的时候不会找了,哎

要细究的话,要看两个值,第一个时该net的cap,可以通过查看该net的属性来得到(相关命令:list_property、get_property,我这里说的是EDI的,ICC用list_attribute、get_attribute)。第二个看lib中该buf的输入pin的cap大小(lib中有)和该buf的output_load参数(目的是让buf后面可以带动的负载有个大致了解)。个人意见

也可以尝试用两个反相器代替插buffer,延迟会小一些

你太纠结了, hold 没问题的话 就选一个较大的buf就可以,hold有问题就选一个中等的,你先修,再返回pt看,慢慢就有经验了,修时序哪需要那么精细 啊,这样不累死了,就粗暴的修,有问题再改呗,你在这纠结的时间都迭代好几次了