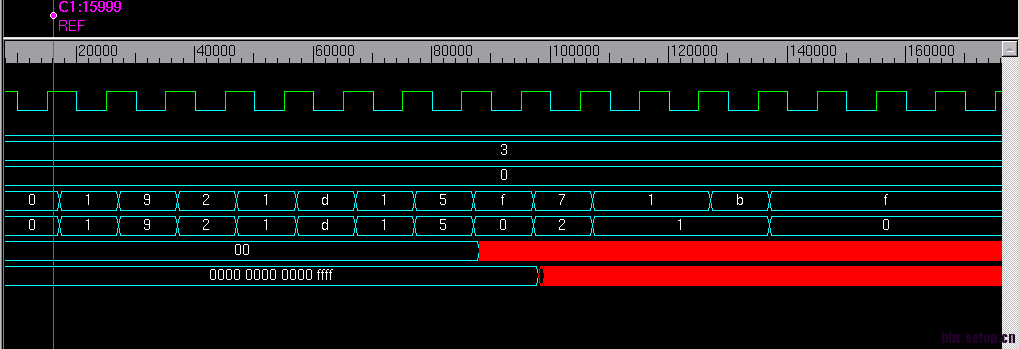

ICC后做后仿发现波形输出除了前面一段以外,后面全是不定态XXXXX

我现在猜想可能是时序有问题,但是如果时序有问题,那输出不可能刚开始有值,后面全是不定态阿。

这种后面全是XXXX的情况是怎么回事呢?是我提参出错了?还是我生成SDF出错呢?我的STA全是通过了。

看看sdf 做做sta 看看, ptread_sdf ,

还有查下出问题的具体路径, 看看时序slack,有时候是timing 余量不大造成的,尽管是过了STA

建议APR 留的余量大些,

sdf反标之后的动态仿真,如果有timing violation应该有 warning报出,如果是从warning开始的仿真时间之后全部x,则是timing violation造成notifier翻转造成,在仿真器参数中加入no_notifier在进行仿真,既可避免出现x,violation信息还是会继续报出。

恩,之前是直接read_parasitics对PT中的设计反标的RC参数,然后生成SDF去做后仿。今天又尝试把PT生成的SDF重新反标到PT中的设计,然后再report,有如下结果。这里有个问题就出现了,为什么由PT生成的SDF文件中没有transition的反标呢?PT生成的SDF应该是来源于parasitics吧

max_delay/setup0.00(MET)

min_delay/hold0.00(MET)

recovery0.00(MET)

removal0.00(MET)

sequential_clock_pulse_width0.00(MET)

min_period0.00(MET)

Warning: Transition times on not annotated delay arcs havebeen set to zero. Cannot perform max_transition checking. (PTE-057)

max_capacitance0.00(MET)

max_fanout0.00(MET)

从仿真波形上明显看出,VCS报hold time violation的地方并不是我出现XXXX很多的地方,出现XXXX大概是在80000,所以就不是您说的报warning就出现XX的情况。按照你的要求,我在simulator的时候选项中已经加入了-no_notifier了,但是却有下面的warning。

Warning:unknown flag: '-no_notifier' ignored

Chronologic VCS simulator copyright 1991-2008

Contains Synopsys proprietary information.

Compiler version A-2008.09; Runtime version A-2008.09;Sep 11 12:18 2011

Doing SDF annotation ...... Done

VCD+ Writer A-2008.09 Copyright 2005 Synopsys Inc.

File /.../inter.vpd is opened successfully.

testbench.v, 54 :#30 $stop;

"smic13g.v", 18775: Timing violation in testbench.TOP1.add1_ext_reg_reg_12_

$hold( posedge CK &&& (flag == 1'b1):16000, negedge D:16000, limit: 500 );

"smic13g.v", 18775: Timing violation in testbench.TOP1.add1_ext_reg_reg_13_

$hold( posedge CK &&& (flag == 1'b1):16000, negedge D:16000, limit: 500 );

"smic13g.v", 18775: Timing violation in testbench.TOP1.add1_ext_reg_reg_14_

$hold( posedge CK &&& (flag == 1'b1):16000, negedge D:16000, limit: 500 );

"smic13g.v", 18774: Timing violation in testbench.TOP1.acc1_reg1_reg_2_

$hold( posedge CK &&& (flag == 1'b1):26000, posedge D:26000, limit: 500 );

"smic13g.v", 18774: Timing violation in testbench.TOP1.add1_ext_reg_reg_9_

$hold( posedge CK &&& (flag == 1'b1):56000, posedge D:56000, limit: 500 );

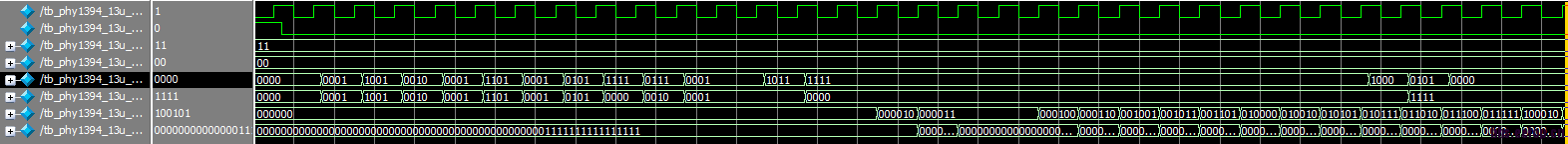

正确的时序仿真图在做原型验证的时候应该如下:

求问这是怎么回事呢?

我的STA结果如上面已经给出了。

sdf 反标PT 以后, transition, load 信息是没法反标的

要通过 set_annotated_transition/ set_annotated_capacitance / set_annotated_resistance

来反标上去,

因此 SDF flow 只能检查timing,trans/load 信息要另外加上去,

有点麻烦

恩,一直很感谢你的细心回答。关于上面提到的VCS后仿问题,今天搞明白了。原来是因为在VCS做编译过程的时候没有添加+maxdelay这个选项(modelsim里面是可以在GUI上找到,所以之前说modelsim通过了),而VCS默认是提取typical的参数,所以,加上这个选项就正确了。

另外就是请教一下,你提到的PT中反标SDF文件,之后需要手动反标transition、cap、load这个东西,这些东西的参数是从哪能找到呢?是ICC输出的什么文件吗?这个我在ICC中找了一下貌似没有找到。

这样的,

pt 读入spef, 然后要得到各个pin,net的属性吧, 是

actual_transition_rise ,total_capacitance 等, 用

get_attribute 得到, 然后再写出来

set_annotated_transition/capcaitance/resistanceXXXX

比较麻烦,我记得以前是这么干的,

如果直接用spef 做sta flow ,就没这个问题了, trans/load 信息都有的

sdf 不一定是pt产生,还可以用ets, 等工具来产生

LZ,我遇到和你同样的问题,请问你是怎么解决的

我也遇到这个问题了,在命令里加入+maxdelay,提示“Unknown compile time plus argument 'maxdelay' is ignored.”,请问楼上都是怎么解决的?

因此 SDF flow

不知您后仿真过了吗? 我目前后仿真还是有不定态 不知道小编说的+maxdelay是什么意思啊? 是在TB中加还是属于vcs的一个选项,启动的时候加呢。功能验证是过了,时序也没问题,后仿真去掉notimingcheck就出现了不定态 感觉时序也没问题。不知道问题出现在哪里。