门控时钟为不定值

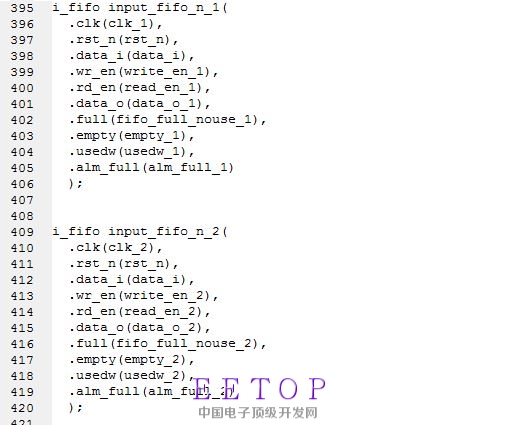

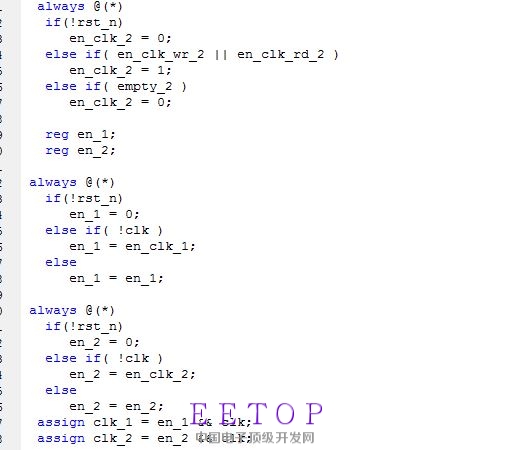

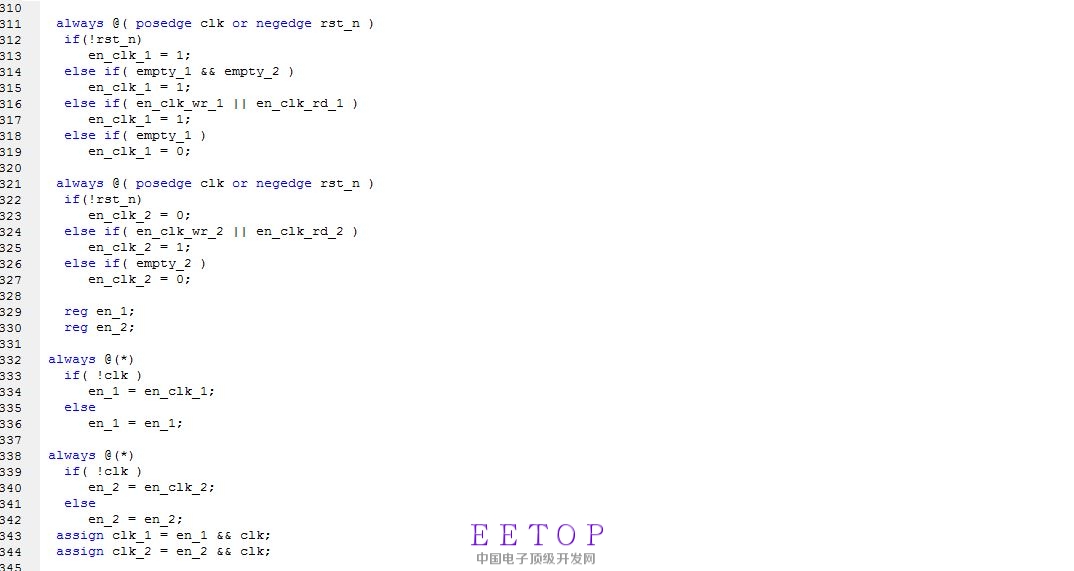

上面是我的截图,大家给我解决一下哈

在前端板块你也在问这个问题,看到你的代码基本明白了。

en_clk_1和en_clk_2不要用latch,

always @ (posedge clk or negedge rst_n)

begin

if (!rst_n)

en_clk_2 <= #DLY 1'b0 ;

else if (A)

en_clk_2 <= #DLY 1'b1 ;

else if (B)

en_clk_2 <= #DLY 1'b0 ;

end

always @ (*)

begin

if (!clk)

en_clk2 <= en_clk_2

end

真的非常感谢你,为什么不用latch呢?这跟不定值有关系么?

刚刚试了试,代码改为现在这样了,可是还是为不定值,我吧仿真图放上来了,你有空的时候帮我看看好么?

这是那个时钟最开始的时候的波形,上面还有一个波形,这个的主要的问题是即使发现en_1复位信号拉高时为1时,即使en_1信号为高电平,clk_1也还是红色的状态,很奇怪。

用latch时序分析会直接晕菜,除开clock gating,所有的数字逻辑要避免产生latch。从给的波形无法分析问题,你用FIFO的读写使能去门控时钟其实没有完全必要,你就让时钟常在,FIFO只有在读写使能有效的时候才会去动作

我的本意是降低功耗,可是不加门控时钟的话,只控制使能不是还有时钟负载这样的功耗么,这样我的功耗达不到要求啊。

你多虑了,综合时使用-gate_clock这个参数,DC工具会自动把符合条件的DFF的clock生成带门控的时钟,不需要在设计里纠结每个小模块的gating问题。RTL里需要通过gating来考虑功耗的,一般只针对整个IP,比如在不需要这个IP工作时,把整个IP的clock采用门控gating掉。

也就是说我用两个FIFO,当一个FIFO不用的时候我将它关掉,可能跟没关掉前的功耗一样喽?好惨

没错,功耗差别微乎其微,因为没有工作的FIFO,由于读写使能都为0,相应DFF的clock都是gating住的,所以小编不要在很小的模块级别去考虑时钟gating带来的功耗节省,这不是重点。

比如FIFO的写入:

always @ (posedge clk)

begin

if (wr_en)

fifo_buffer[addr] <= #DLY data_in ;

end

像这种不带else逻辑的DFF,综合出来的结果就是用wr_en去门控产生DFF的CK端,data_in直接连到DFF的data端。如果你的FIFO此时没有工作,wr_en为0,时钟自然就是被gating住的

但是FIFO还有读指针计数,写指针计数,还有usedw计数,这些应该也有功耗吧。

你的指针不是一样只在读写使能有效时才加减么?指针DFF的CK一样会被读写使能门控。你RTL设计都考虑到DFF级别的时钟门控了,太过了。使用always描述的DFF,只要有if没有else的条件,就可以综合成带CK gating的DFF,用不着人为设计每个DFF的clock gating