pad处的floating pin如何处理

时间:10-02

整理:3721RD

点击:

derive_pg_connection -power_net VDD -ground_net VSS -create_ports top

derive_pg_connection -power_net VDDIO -ground_net VSSIO -create_ports top

derive_pg_connection -power_net VDD -power_pin VDD -cells [get_flat_cells *] -reconnect

derive_pg_connection -ground_net VSS -ground_pin VSS -cells [get_flat_cells *] -reconnect

derive_pg_connection -ground_net VSSIO -ground_pin VSSIO -cells [get_flat_cells *] -reconnect

derive_pg_connection -power_net VDDIO -power_pin VDDIO -cells [get_flat_cells *] -reconnect

然后preroute_instances的时候 很多提示,如下:

WARNING:Failed to make a connection for the following pin:

((2210.315, 4919.180) (2210.325, 4929.180)) (Net: VSS)(wire on layer: M9 [19])

[2174] pfiller2161

WARNING:Failed to make a connection for the following pin:

((2322.325, 4919.180) (2322.335, 4929.180)) (Net: VSS)(wire on layer: M9 [19])

[2175] pfiller2162

[2176] pfiller2163

[2177] pfiller2164

[2178] pfiller2165

[2179] pfiller2166

[2180] pfiller2167

[2181] pfiller2168

等等

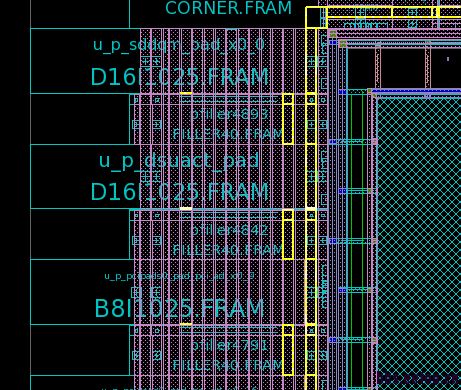

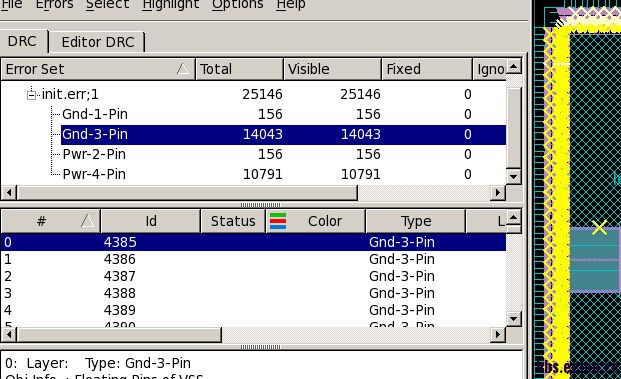

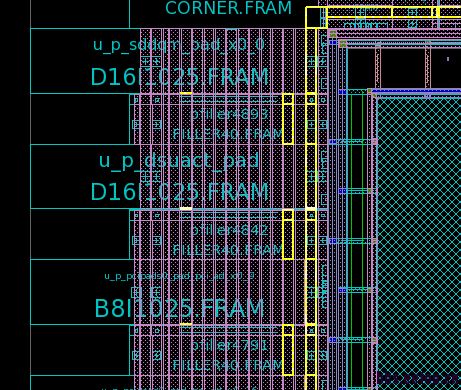

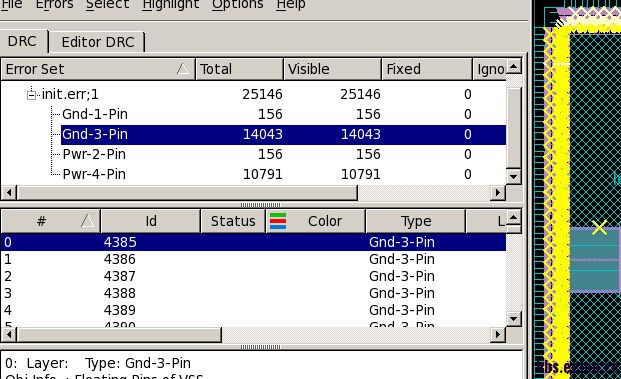

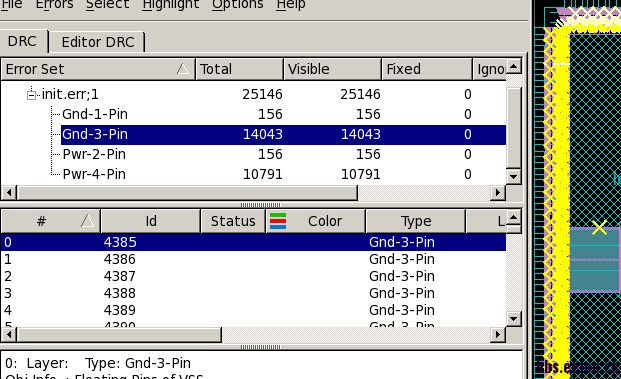

然后在verify_pg_nets的时候在pad处很多违例,如下:

derive_pg_connection -power_net VDDIO -ground_net VSSIO -create_ports top

derive_pg_connection -power_net VDD -power_pin VDD -cells [get_flat_cells *] -reconnect

derive_pg_connection -ground_net VSS -ground_pin VSS -cells [get_flat_cells *] -reconnect

derive_pg_connection -ground_net VSSIO -ground_pin VSSIO -cells [get_flat_cells *] -reconnect

derive_pg_connection -power_net VDDIO -power_pin VDDIO -cells [get_flat_cells *] -reconnect

然后preroute_instances的时候 很多提示,如下:

WARNING:Failed to make a connection for the following pin:

((2210.315, 4919.180) (2210.325, 4929.180)) (Net: VSS)(wire on layer: M9 [19])

[2174] pfiller2161

WARNING:Failed to make a connection for the following pin:

((2322.325, 4919.180) (2322.335, 4929.180)) (Net: VSS)(wire on layer: M9 [19])

[2175] pfiller2162

[2176] pfiller2163

[2177] pfiller2164

[2178] pfiller2165

[2179] pfiller2166

[2180] pfiller2167

[2181] pfiller2168

等等

然后在verify_pg_nets的时候在pad处很多违例,如下:

VDDIO/VSSIO 属于external net,pad filler加入以后就全abut起来了,

pr只对内部VDD,VSS 来做就行了, 删除所有VDDIO/VSSIO的derive情况,

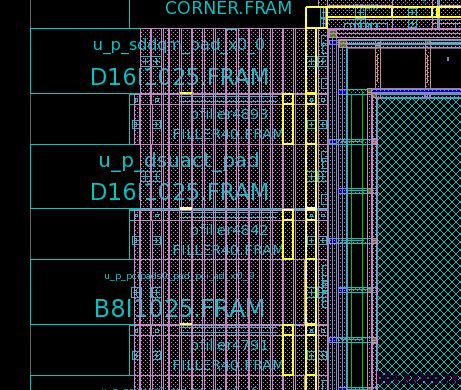

感觉是自己摸索啊,路走的很弯小编,我去除VDDIO VSSIO之后,我又重新preroute了下,结果还是有floating pin 只不过没有VDDIO 和VSSIO的floating pin了,但还是有VDD和VSS的floating pin

不知道怎么个情况ignore吧,等calibre再说了,

padring上怎么会有pg ring的,表示很奇怪,