关于level shifter的一个问题

set_level_shifter ls_out -location parent -domain PD_ADD -rule both -applies_to outputs

DC工具不是根据UPF的描述自己插入level shifter吗,为什么上面设置之后,check_mv_design还是出现这样的warnings

Warning: Pin 'I_PWR_CTRL/sr_ctrl_reg/Q'(VDD[1.08v]) cannot drive 'I_ADD/U32/INP'(VDD1[0.70v]) due to voltage differences (effective strategy is [rule = both, threshold = 0.00]). (MV-231)

PD_ADD是一个power domain,TOP是另一个domain,总共就这两个;由TOP这个domain的信号驱动PD_ADD这个domain中的一个cell,为什么没有在PD_ADD这个domain的内部insert level shifter呢?

DC 有时候会发呆,

建议再来一次 insert_level_shifters

我试过这个的,不行,insert_level_shift会报错,说

Error: The insert_level_shifter command is not supported in the UPF mode. (UPF-002)

那就自己写脚本,手工加 level_shifter buffer 好了。

你是说用命令 insert_buffer来加吗?

insert_buffer 不行的话,就create_cell disconnect_net connect_net

我试下

insert_buffer不行,因为level shifter cell不是buffer或者inverter;

你说的第二个方法,是create_cell

status create_cell

cell_list

[reference_name]

[-logic 0 | 1]

[-only_physical]

这个只是在current design中创建一个cell,具体这个cell放在哪里,连接哪根net并不能指定,所以对解决我的问题貌似没有用

create_cell disconnect_net connect_net

---

要一起用 ~

写个小的proc

create_cel level_shift_addr_0 lvl_9t

disconnect_net addr_0 pd1/addr[0]

create_net lvl_addr_0

connect_netlvl_addr_0 "pd1/addr[0] level_shift_addr_0/in"

connect_net addr_0level_shift_addr_0/out

大致如此 ~

明天再试试吧;要回去了;

我刚看了下,connect_net只能在同一level层次将net和pin/port进行连接,因为我的这条net是acroo两个电压阈的,或者说这个net连接着两个cell,cell1,cell2,cell1在一个block1中,cell2在一个block2中,我即使disconnet这条net之后,貌似也不能通过connect_net进行连接成功

貌似也不能通过connect_net进行连接成功

---

用 connect_pin

插入成功,但是check_mv_design -level_shifter 时候,报warnings-->

Warning: Found 1 level shifter(s) not conforming to level shifter insertion strategy. (MV-213)

Warning: Level shifter 'I_ADD/eco_shifter' has main power mismatch violation due to location constraint. (MV-232c)

check_mv_design -level_shifter 时候,报warnings

---

derive_pg 对了吗?

我这是在DC中呢,没有derive_pg_connection

还需要使用connect_supply_net将你插入的LS的power连接好的

你好,我在upf中关于level shifter 的约束是:

set_level_shifter ls_in-domain PD_ADD -rule both -applies_to inputs

set_level_shifter ls_out-domain PD_ADD -rule both -applies_to outputs

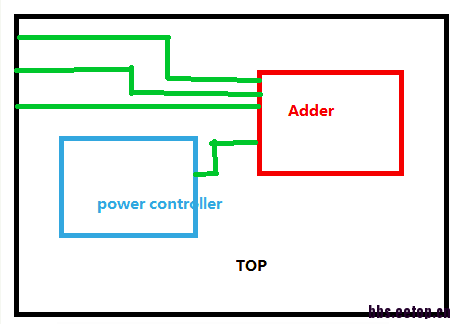

Adder这个是PD_ADD domain,电压是0.7V,剩下的power controller和TOP是PD_TOP这个power domain,电压是1.08V

为什么最后DC综合完之后从power controller这个模块到Adder这个模块的连线没有插入level shifter呢? 从TOP这个模块的port到Adder这个模块的port的连线倒是都插上了level shifter

如果需要connect_supply_net进行连接的话,为什么check_mv_design -verbose只检查出来从power controller这个模块到Adder这个模块的连线没有插入level shifter呢? 那其余地方的也该能检查出来才对吧

set_level_shifter ls_in -location self -domain PD_ADD -rule both -applies_to inputs

set_level_shifter ls_out -location parent -domain PD_ADD -rule both -applies_to outputs

DC工具不是根据UPF的描述自己插入level shifter吗,为什么上面设置之后,check_mv_design还是出现这样的warnings

Warning: Pin 'I_PWR_CTRL/sr_ctrl_reg/Q'(VDD[1.08v]) cannot drive 'I_ADD/U32/INP'(VDD1[0.70v]) due to voltage differences (effective strategy is [rule = both, threshold = 0.00]). (MV-231)

PD_ADD是一个power domain,TOP是另一个domain,总共就这两个;由TOP这个domain的信号驱动PD_ADD这个domain中的一个cell,为什么没有在PD_ADD这个domain的内部insert level shifter呢?

DC 有时候会发呆,

建议再来一次 insert_level_shifters

我试过这个的,不行,insert_level_shift会报错,说

Error: The insert_level_shifter command is not supported in the UPF mode. (UPF-002)

那就自己写脚本,手工加 level_shifter buffer 好了。

你是说用命令 insert_buffer来加吗?

insert_buffer 不行的话,就create_cell disconnect_net connect_net

我试下

insert_buffer不行,因为level shifter cell不是buffer或者inverter;

你说的第二个方法,是create_cell

status create_cell

cell_list

[reference_name]

[-logic 0 | 1]

[-only_physical]

这个只是在current design中创建一个cell,具体这个cell放在哪里,连接哪根net并不能指定,所以对解决我的问题貌似没有用

create_cell disconnect_net connect_net

---

要一起用 ~

写个小的proc

create_cel level_shift_addr_0 lvl_9t

disconnect_net addr_0 pd1/addr[0]

create_net lvl_addr_0

connect_netlvl_addr_0 "pd1/addr[0] level_shift_addr_0/in"

connect_net addr_0level_shift_addr_0/out

大致如此 ~

明天再试试吧;要回去了;

我刚看了下,connect_net只能在同一level层次将net和pin/port进行连接,因为我的这条net是acroo两个电压阈的,或者说这个net连接着两个cell,cell1,cell2,cell1在一个block1中,cell2在一个block2中,我即使disconnet这条net之后,貌似也不能通过connect_net进行连接成功