SDRAM Timing report

各位大神,求助一个综合是越到的SDRAM问题,下面是详细问题描述。

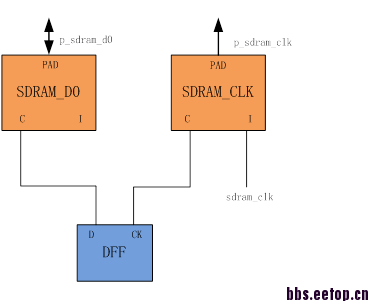

电路描述:

1.

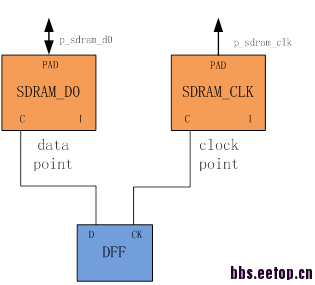

下图中的电路是SDRAM input采样结构,其中SDRAM_D0和SDRAM_CLK分别是SDRAM的数据和时钟PAD,DFF是p_sdram_d0输入第一级采样flip-flop。

2.

时钟定义中,把sdram_clk定义为源时钟,sdram_clk_pad定义为generated clock。dc::create_generated_clock –name “sdram_clk_pad” –source sdram_clk \

–divide_by 1 [dc::get_portsp_sdram_clk]

3.

input/output delay根据sdram_clk_pad设置。

dc::set_input_delay –clock sdram_clk_pad –add_delay –max/minxxx \

[dc::get_portsp_sdram_d0]

SDRAM input circuit

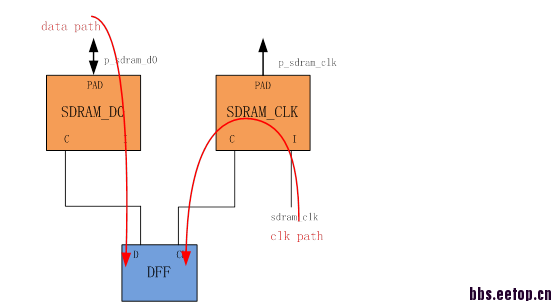

问题描述:

根据上述设置,我们认为clock和data path应该如下图。

Clock and Data path

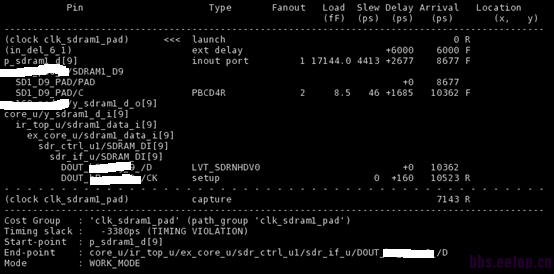

但是在RC中的timing report发现了从p_sdram_d0到第一级dff(DOUT_hP_reg_)时出现了timing slack violation的情况,是因为没有在clock path加入delay引起的。

Input timing violation

在RC中也能报出从p_sdram_clk到DFF采样clock的path,如下图。

Clock path timing report

所以怀疑是RC report时没有加入clock path的delay。请问是我们设置的有问题还是report的有问题?

自己顶一下,难道RC的timng report中不给clock path算delay吗?

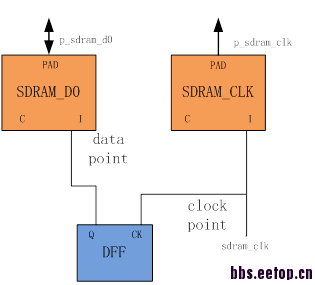

解决方法:

经过尝试发现RC在reporttiming的时候clock path被认为是ideal network,在clock path上面不会加任何delay。而我们的目的是约束PAD和DFF之间不要存在太大的组合逻辑,所以使用一种变通的方法。

1.

对于set_output_delay,定义clock为sdram_clk,data指定为SRAM_DO/I。只约束从DFF到PAD/I的路径,认为clock和data经过SDRAM_CLK和SDRAM_D0 PAD的delay是一致的。

2.

对于set_input_delay,定义clock为SDRAM_CLK/C,data指定到SDRAM_D0/C上。只约束从PAD/C到DFF的路径,认为clock和data经过SDRAM_CLK和SDRAM_D0 PAD的delay是一样的。

在RC综合的时候可以这么设置,在给后端的sdc中再把input/output delay设置的端点定义到PAD上,这样能够报出真实的延时信息。

也有朋友帮我出主意,在pad定义clock之后使用set_clock_latency的方式来替代PAD内容的delay。我觉得这种方法也是可以的,主要目的是能够约束PAD和DFF之间的组合逻辑。