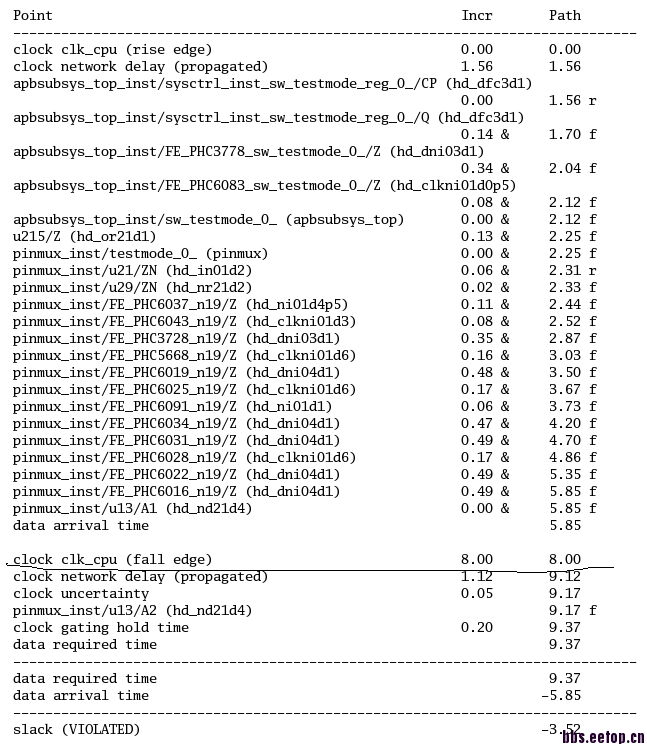

hold time违例的解决办法

看名字clock gating 只用了一个 nand gate, 这种情况只要 CK 是高电平的时候 EN 抵达hold就违例了,所以catch clock要从fall edge 开始。

现在clock gating一般都是ICG,就算自己搭一般也加个latch来去glitch

非常感谢您的回复,我设置的就是insert_clock_gating,那我现在这种情况是需要手动再去添加latch来fix这个违例,还是可以忽略不计?

一般这种情况,是在nand gate前面添加latch吗?

谢谢!

这种应该可以忽略的,跟前端沟通一下,可能这个门控后的信号要等好几拍才能稳定被后边逻辑使用,有毛刺也无所谓了。如果前端有要求,那就改代码吧,制定ICG单元

既然DC是你做的,当然不可忽略。

man一下set clock gating style, 然后search "integrated"

DC中的约束是前端给的,关于clock gate的设置为:

set_clock_gating_style -sequential_cell latch -minimum_bitwidth 4 -pos {integrated} -control_point before

insert_clock_gating

set_clock_gating_check -setup 0.2 -hold 0.2 [all_clocks]

latch的添加是DC自动的,我想请问下,如果需要手动添加,该怎么手动添加?

谢谢!

就是通过这个命令控制。

如果非要自己加,create_cell, disconnect_..., connect_..., identify_clock_gating

有了这个命令控制,却还有violated,这样的该怎么修呢?