锁存器 时序分析

时间:10-02

整理:3721RD

点击:

各位前辈:触发器的时序分析 是 以时钟延为基准,那么锁存器的 建立时间 保持时间 怎么分析,以什么为基准?

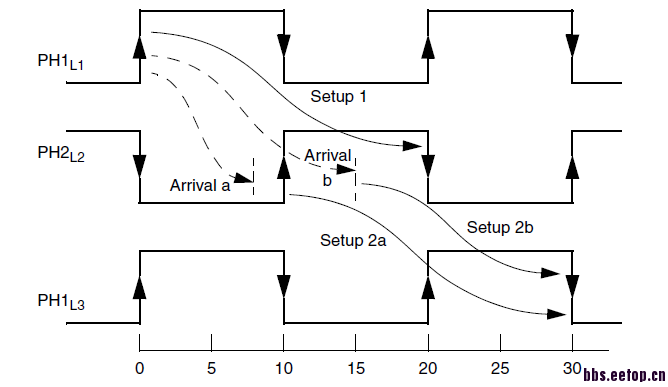

If the data arrives after the opening edge of PH2 (Arrival b), the first path (from L1 to L2) borrows time from the second path (from L2 to L3). In that case, the launch of data for the second path occurs not at the opening edge, but at the data arrival time at L2, at some time between the opening and closing edges of PH2. This timing requirement is labeled Setup 2b. When borrowing occurs, the path originates at the D pin rather than the G pin of L2.

For the first path (from L1 to L2), PrimeTime reports the setup slack as zero if borrowing occurs. The slack is positive if the data arrives before the opening edge at time=10, or negative (a violation) if the data arrives after the closing edge at time=20.

hold check

To perform hold checking, PrimeTime considers the launch and capture edges relative to the setup check. It verifies that data launched at the startpoint does not reach the endpoint too quickly, thereby ensuring that data launched in the previous cycle is latched and not overwritten by the new data.

各位前辈:

触发器的时序分析 是 以时钟沿为基准,那么锁存器的 建立时间 保持时间 怎么分析,以什么为基准?

也是时钟沿,打开latch的lib看就知道了

latch time borrowing, 同时说明了setup如何check,详见pt ug

If the data arrives after the opening edge of PH2 (Arrival b), the first path (from L1 to L2) borrows time from the second path (from L2 to L3). In that case, the launch of data for the second path occurs not at the opening edge, but at the data arrival time at L2, at some time between the opening and closing edges of PH2. This timing requirement is labeled Setup 2b. When borrowing occurs, the path originates at the D pin rather than the G pin of L2.

For the first path (from L1 to L2), PrimeTime reports the setup slack as zero if borrowing occurs. The slack is positive if the data arrives before the opening edge at time=10, or negative (a violation) if the data arrives after the closing edge at time=20.

hold check

To perform hold checking, PrimeTime considers the launch and capture edges relative to the setup check. It verifies that data launched at the startpoint does not reach the endpoint too quickly, thereby ensuring that data launched in the previous cycle is latched and not overwritten by the new data.

好地方,要常来看看

谢谢,了解了

小编什么都懂哈。厉害

谢谢,我看了PT中的说明了,按我的理解:如果锁存器是高电平有效,那么检查的时钟沿下降沿,低电平有效检查时钟沿上升沿。

是这样吗?

是这么检查的,不过锁存器时序分析时可以借用上一个时钟周期的时间,这个和DFF很不一样的,STA复杂

周润德的数字集成电路设计讲的很清楚

IOCELL上有PVDD,PGND端口和VDD,GND端口;这两组端口我本来就是要把他们连在一起的

发错地方了

好久没回来了,谢谢,大神的解答