cts之后对set_input_delay -clock clk的影响

时间:10-02

整理:3721RD

点击:

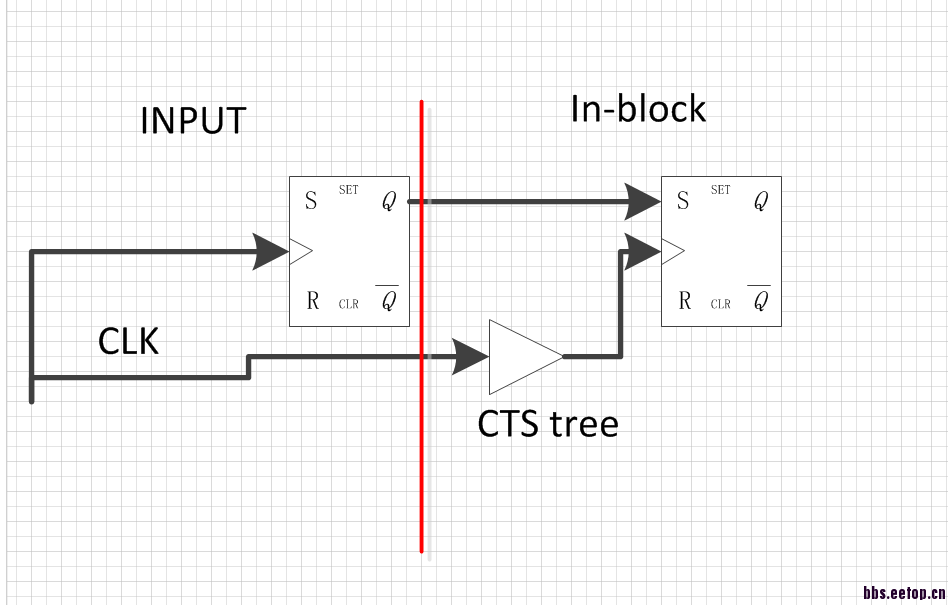

在完成block级别的cts之后,clk到ck会插入buffer,存在latency延迟。

但对于input到reg的路径,因为input路径被set_input_delay -clock clk约束,因此约束的clk是ideal的,没有latency,在cts和cts之后,工具的在计算这种路径时是存在问题的,

请问应如何处理这种情况?

会有什么问题?是 block 外的 clock ideal 又不是 block 里的 clock ideal

因为这个block将来要到soc层面上去应用,也就是说外部的clk会因此而做到和内部clk一样的latency所以我在block level的时候,想把这个外部clk的latency考虑进去,不然会分析in2reg路径会有偏差。甚至是violation

那就把这个 latency 加到 input_delay 分析咯,分setup 和 hold, 优化的时候就不必考虑了吧(相当于额外加了 margin,不然考虑进去迭代应该也可行)。我的经验太少,从来不管。

过约束就好了, io timing要 top flatten看才比较清楚