做完CTS后Debug clock 发现clockTree没连线怎么回事?

时间:10-02

整理:3721RD

点击:

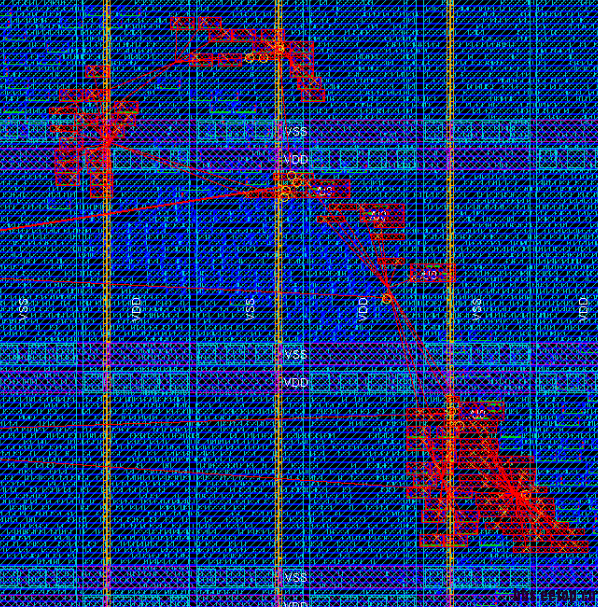

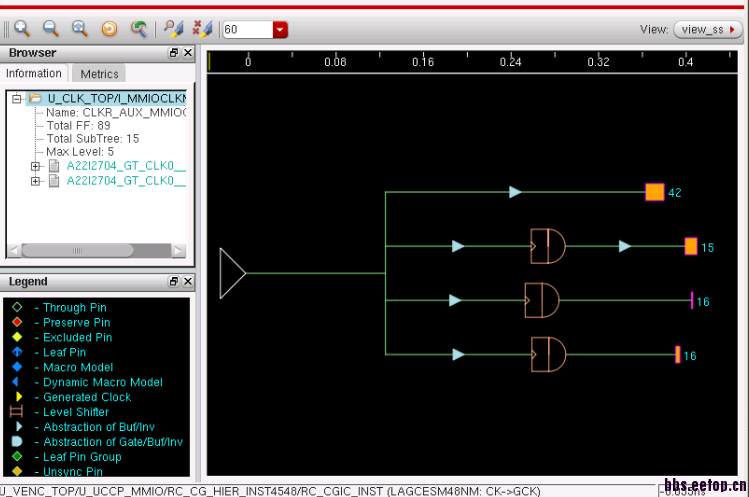

希望能者帮忙解决,请看下图第一个图就是没有连线的clockTree ,感觉sink端之间只有filghtline连接

有route_zrt_group吗?

请问route_zrt_group是什么意思?我使用的是EDI,你说的是ICC上的东西吧?在EDI中该怎么讲?

谢谢指点

哦 那我 不清楚 回复错了 EDI的东西忘记了

好的,谢谢小编热心帮忙,同时请教其他高手,能不能帮助在下解决此问题

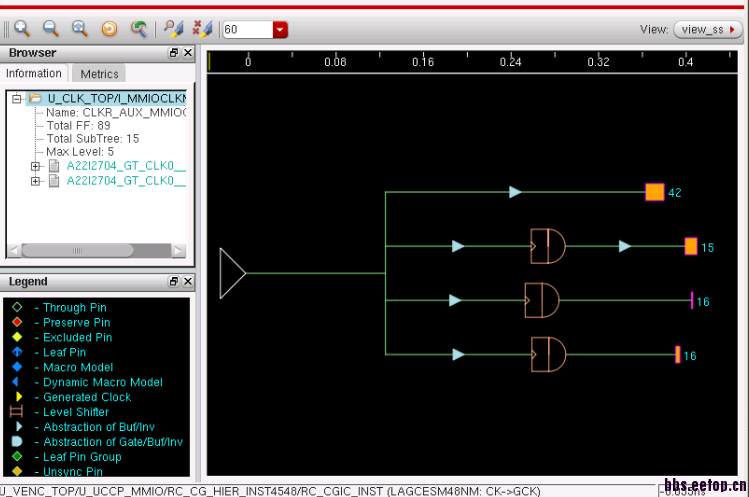

用clock spec 文件了么?用的话就在产生的spec 文件中加入有一个route clock net 的option脚本中也有下面这个变量设置成true。setCTSMode -routeClkNet true

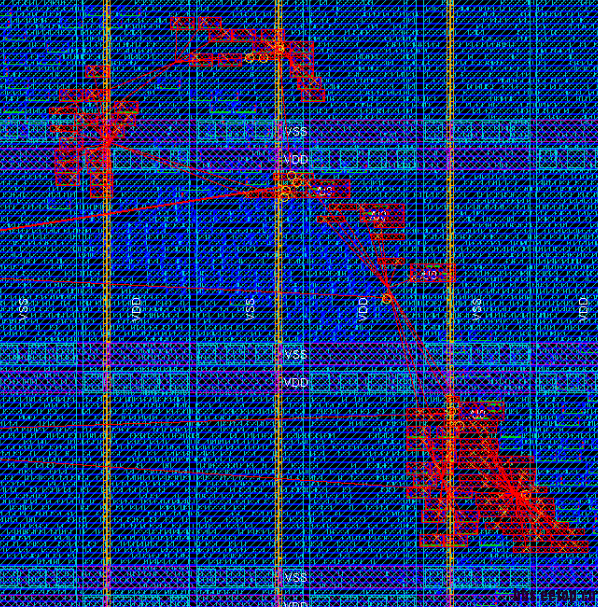

谢谢,您的回复,SPEC文件中设了RouteClkNetYes ,我们把lef中对cell重复定义的内容删除后,CTS绕线就好了,这是什么原因啊?CTS绕线与cell重复定义有什么关系

可能有错误就没有做某些工作了,我不熟edi,猜的哈