timing violation求解!

时间:10-02

整理:3721RD

点击:

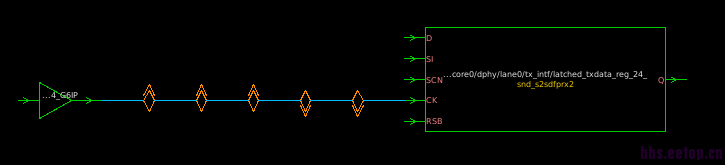

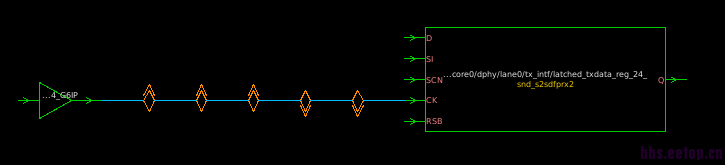

我已经完成clock synthesize,进行timing check有violation。主要是input port到reg的问题,clock1的clock tree上的reg/ck到它的前一级cell( A)之间的net的capacitance比较大,我认为可能是这个原因导致reg的delay比较大,从而使得clock latency比较大,导致timing violation。之前有同事做过这个design,他的结果就比较小。我尝试在reg/ck前插buffer,slack得到改善,但是不明显。请问大家可能是什么原因导致这种情况?怎样缩短clock latency?非常感谢!(reg和A的连接如图)

会不会是设置的input delay比较大?

我这边设置的是0。而且之前也是这么设的。

input port和clock的相互关系不确定,你设置一点input delay试一下呢?

是因为这个reg的place 位置引起的,还是CTS时候没有做好这个clock tree呢?

找到原因了,是因为一条net的fanout太大了。

一条net的fanout太大了。

找到原因就好,你是怎么发现的?

别人告诉我的。而且报表上也有,因为timing report太多了,当时也没有注意看到。

timing有问题,我一般都是修改一下DC的constranits,修改clock uncertainty, input delay,set load,set max fanout这些。以后有问题多多交流吧。

report我觉得report_constraint -all_violators这个必须得看。

你没有设set_clock_tree_options max_fanout ?

设了32。