请教congestion严重情况下的floorplan问题

时间:10-02

整理:3721RD

点击:

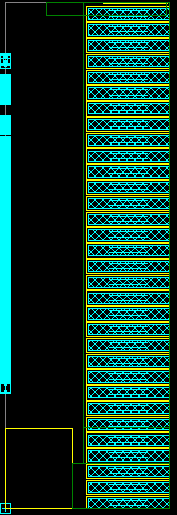

现在在试做一个block的数字后端, 该block的congestion比较严重。

此外,该block中有许多sram,大约占初版floorplan的一半面积。

目前sram的摆放是简单的排成一个长条状,放置在block右侧 如图所示。

如果想改善congestion的问题,请教一下floorplan在哪些方面改善会比较有效果?特别是sram的摆放有什么技巧吗?

图貌似看不着啊?

编辑了一下,现在能看到了么?

sram放成3列,使得std cell部分的现状接近正方形

正解

感谢!

确实哈

是不是和摆放几列关系不大,关键是摆成接近正方形的样子?

为什么摆放成正方形就能减少congestion,是因为接触面增大了吗?

让std cells的部分接近正方形?是把std cells和sram分开放,一个占左边一半,一个占右边一半地放吗?

这样感觉不太好啊~sram出pin的宽度只有原来的三分之一了啊

我的理解:摆成正方形的,可以让metal的布线更方便。如果是长的竖条状的话,就像小编图片所示。假设是三层金属布线,那么M2的走线就非常多,M3利用率就会不高,那么就会比较拥挤。陈版的每日一题中有类似题目。

如果是四层金属,1~4层呢?也需要做成方形的吗?

如果是四层金属,1~4层呢?也需要做成方形的吗?

还有为什么metal 2的走线多了,metal 3的利用率就低了呢?