partition问题,来个好心人帮帮忙啊!

我现在的步骤是:

(1)对每个子模块specify partition

(2)asignPin,place,trialRoute

(3)commit partition勾选了retain Top-level Routing on Top-level Design

(4)savePartition,生成了子模块和顶层模块目录

(4)然后进每个子模块的目录运行encounter,完成布局布线

(5)重新encounter,导入之前的ploorplan,运行partition(6)change partition view 分别导入子模块的def文件,最后导入顶层的def文件

(7)unpartition

问题来了:我的顶层没有模块之间的连线了,这个本来就是需要自己连的吗?还是哪里不对?然后verify geometry的时候出现白色XX,我在子模块检查的时候没有啊,有没有什么办法修正?

我想知道我的流程对不对,有没有漏什么东西?请详细一些,第一次做不是很熟,小弟跪谢了!

你顶层是不是没有进行nanoroute和插welltie,fill,dcap的操作啊。

我的顺序一般是(SE+ICC,供参考):

(1)import .v files,导入顶层def(如果有顶层def,没的话需要自己设置尺寸和刷电地,然后摆pin)

(2)specify partition & place standard cells(floorplan mode,取消place I/O,因为之前已经摆好pin了)

(3)trial route(floorplan mode),assign pin,legalize pin,estimate routing channel

(5)commit partition & save partition

(5)然后进每个子模块的目录运行encounter,将def转成5.5版本(只保存floorplan),用于icc的P&R

(6)每个子模块做完做顶层拼接。(在partition保存的的顶层目录下启encounter,进行nanoroute(global route & detail route,可以设置绕线层,还可以设置致绕哪些线,timing 和 congestion的trade off等),删掉电地,到出一个gds,插welltie,fill和dcap,删掉子模块,到处dcap的gds。)

(7)将两个gds导入virtuoso,将两张版图叠在一起,罩上电地,完成顶层。

合并的话用的是Assemble Design

谢谢你,可是我在做顶层nanoroute的时候,他会把子模块的布线给打乱,请问这是怎么回事呢?

谢谢你,可是我在顶层做nanoroute之后,会把子模块的布线给打乱,这是什么原因呢?

我用assemble做的话,做时序分析的时候,所有的路径都为N/A,请问这样做有什么要点需要注意的啊?

内部的布线被打乱?不应该啊。

你Assemble Design之后有做的nanoroute?

我没在Assemble Design之后做过nanoroute,Assemble Design之后都是做的timingAnalysis。

nanoroute应该在top-level design做吧?

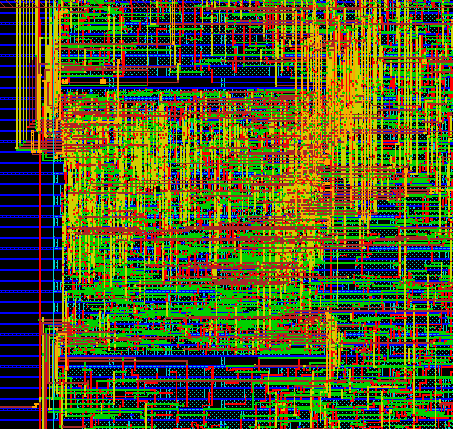

我 use assembeDesign to assemble top and block design之后设计就被flattening了,怎么才能 使black成为一个像IP核一样的东西。我assembeDesign 之后的结果:

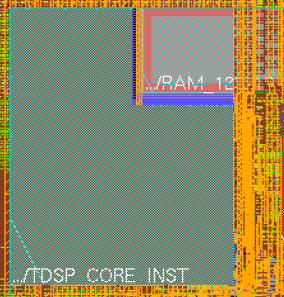

我看别人的结果应该是:

求大神指点,谢谢!我挺急的。