给时钟IO加PAD的问题

时间:10-02

整理:3721RD

点击:

大家好我DC综合前,在RTL中给IO PORT加PAD

综合后,做floorplan的时候,读入网表,保存设计的时候就出现错误

时钟PAD有电源和地。我例化的时候没有考虑,默认把VDD GND都初始化为0了

网表中没有电源端口,我在fp中才创建

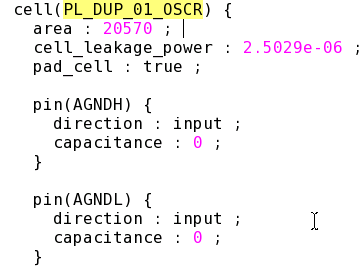

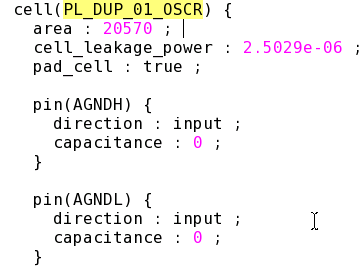

PAD的mw库文件描述如下

请问这个问题要怎么解决呢

VDDH VDDL这里显示的总是

connect 0 power and 0 ground ports

电源地这里总感觉好模糊啊

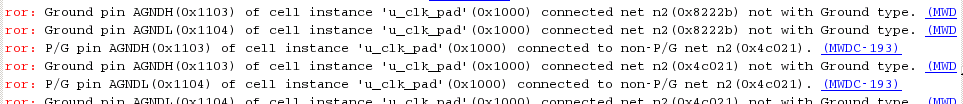

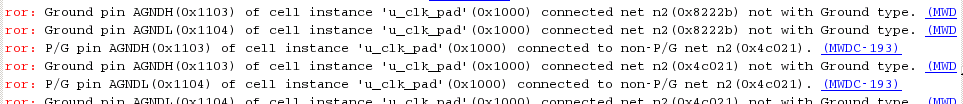

综合后,做floorplan的时候,读入网表,保存设计的时候就出现错误

时钟PAD有电源和地。我例化的时候没有考虑,默认把VDD GND都初始化为0了

网表中没有电源端口,我在fp中才创建

PAD的mw库文件描述如下

请问这个问题要怎么解决呢

VDD怎么能初始化为0能,应该为1吧?

看他综合后的网表里面是0只有时钟PAD有电源脚

这个问题是电源引脚的pin type,不知道可不可以不管

后面执行derive_pg_connection的时候也会出warning

我的IO PAD的电源地引脚有 VDD/GND VDDH/VSSH

标准单元为VDD/GND

时钟电源地为AVDDH/AGNDH AVDDL/AGNDL

运行的脚本为

VDDH VDDL这里显示的总是

connect 0 power and 0 ground ports

电源地这里总感觉好模糊啊

create_cell 创建的VDD GND还有corner cell的电源

总是提示 Not binding the unconnected PG pin ...

有关绑定这里应该怎么做,guide包括lab还有网上怎么都找不到呢