cadence做rail analysis时报错,求助

试了很多种设置,最后剩下这个错误没法解决,只好上来求助各路大神了。

英文意思是看懂了,但是没明白这里的shape指的是什么。

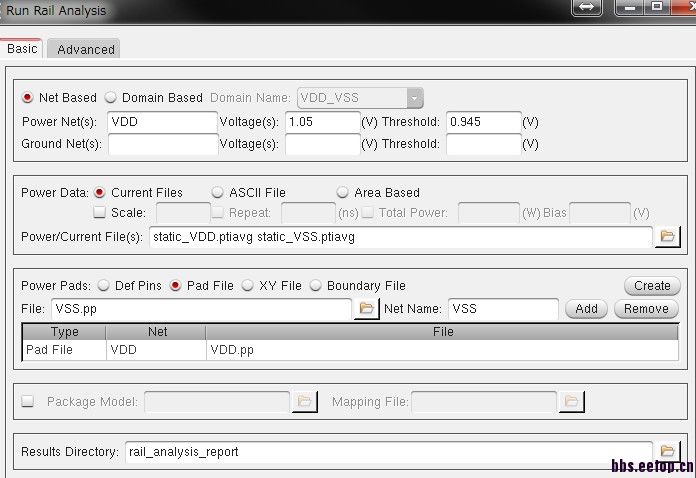

我设置的是想测VDD这个net的IR-drop。

没有detail route

樓上的這跟detail route有甚麼關係嗎?

看一下你的POWER叫甚麼名字是不是不叫VDD

可以試一下打virtual power 在power net 上

谢谢小编的回复!请问detail route是什么啊?

我该如何去做?该参考user guide的哪一部分?或者说用什么关键字来搜索?

要做analysis的这个设计已经完成add filling了。

early rail analysis可以出来个结果。

谢谢你的回复!这个设计已经完成add filling了。

对VDD这个net做early rail analysis可以出来个结果。

“可以試一下打virtual power 在power net 上”

请问这个要怎么做呀?该参考user guide的哪一部分啊?

不是很懂為何加了FILLER就可以做rail analysis除非你沒接follow pin所以POWER是斷掉的然後加FILLER,follow pin就全接起來了

但還是不對呀沒接follow pin M1 rail還是接不到POWER,就算有加FILLER也是power floating,

能告訴我發生甚麼事了嗎?

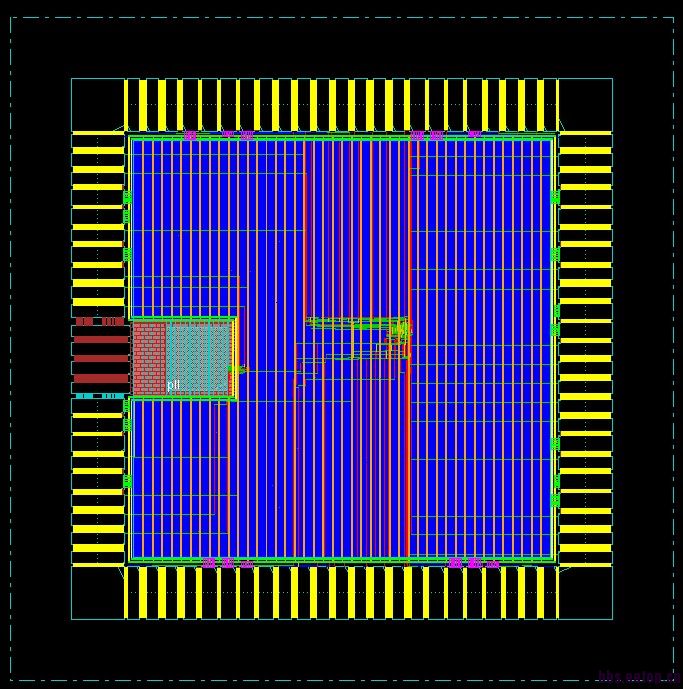

我已经把floorplan-add power ring-global connection-auto placement and routing-CTS-nano route-add filler这一个流程跑下来了。做出来的layout图如下:

rail analysis的设置如下:

我想告诉你所有的细节,但又不知从何说起。

你有使用什么IM工具吗?gtalk、qq、skype之类的,我加你如何?

解决了。有两种可能。

1. 生成power libray时导入的文件错了,导致power library里没有任何数据,所以出错了

2. VDD 的pad file 定义出错了

what is this?云里雾里的!