问个PT的path问题。

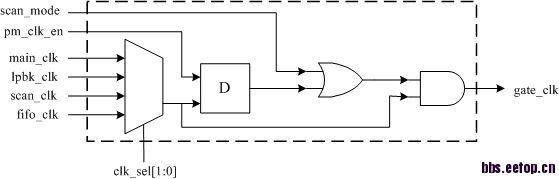

电路中有如图一个自己搭的clk gating cell。在hold check有些flop的时候,发现data的path和clk path经过这个cell的path不一样,所以delay也不一样。data path,PT先了从clk mux直接到最后的gate_clk,而clk path,PT选了经过这个clk enable的flop一级级传到最后面的gate clk. 我知道这样子PT是为了考虑worst case,但实际情况应该不会这样吧,应该经过这个cell的delay一样吧。

请问该怎样设set_case或者别的,才能让pt选择同一条path.

谢谢

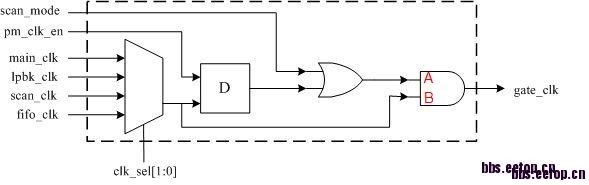

碰到过这种问题,A点其实是gating信号,也就是D出来的路径,功能上来说它不是时钟。B点才是实际时钟路径。

我的做法是disable掉从A点到gate_clk点的路径(试过set false path A点到gate_clk点,好像不起作用),但是要作A和B的clock gating检查。

这个问题原因是PT分析时钟路径时穿过了寄存器,也就是D。我猜小编应该和我一样在gate_clk那个点上generate了clock并且source是clock mux前的,所以gate_clk路径追到source便会穿过D。

不知道有没有更好的方法

多谢回复。我后来又去看了下详细的报告。发现其实PT在最后算的时候,会把clock recovergence time再减去,这样到最后,其实data和clk的path穿过这个clk gating的时间是一样的。但不知道为什么PT要这样子报路径。可能就像你说的这个原因。

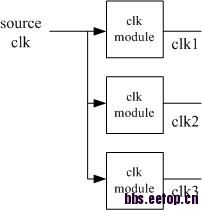

确实如你所言。我在gate_clk处设置了generated_clock, source clk设在mux前了.我现在的情况是source clk很少,只有几个,clk module出来的clock很多。因为我内部的几个主要模块都定义了有单独control的clk,因为这些模块也会工作在不同频率下。另外,这样clk 名字不同,也比较容易PT检查的时候,知道是哪里的path,是不是false path等等。就如下图结构所示。

不知道小编大人有没有什么好的办法介绍。

用ICG cell吧,别用离散gating cell, 这样会简化一些check

多谢小编,可现在已经有些来不及了。请问按照这个样子的design,该怎么设clock,既可以给我的clock分组,又可以让generated clock从source开始check

create_generated_clock -combinationalxxxxxxx

set timing_clock_gating_propagate_enable false

小编你好,我看到你的帖子中有个多时钟端口选择器,我现在也碰到类似的结构,但不知道怎么去用DC综合它,脚本该如何设置。http://bbs.eetop.cn/thread-418126-1-1.html请问你能指点一下吗?多谢了。

综合你只要用最快的频率去综合就可以。

你好,我的32个输入时钟都是同频率的100M,但是这个结构的输出也是时钟,后面还要个二分频电路,反馈到中间的寄存器。请问这种结构该怎么设置脚本呢?该注意些什么?