power network如何设计

在数字电路设计后端工作中,我们需要在Floorplan阶段对整个chip设置好Power network。

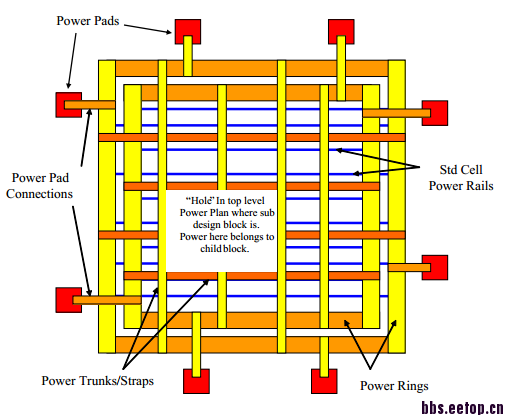

如上图所示,为一个Power network的基本示意图,主要有power pads, power rings, powerstraps, Std cells power rails。

现在的问题是,大家在做Floorplan的时候,是怎么样去设计的了?

具体的就是:power pads应该有几个?

power rings, power straps,Std cells power rails的宽度怎么样去估算?

顶一下

power pad数量根据功耗和 power IO cell可承受的电流决定,同时需要满足ESD的要求,在不影响die size的情况下,可尽量多一点。

power straps也是越多越好,当然前提是不影响routing,不超过max metal density 要求

你好,感谢你的回复,能够说的跟详细一点吗,即: power rings, power straps,Std cells power rails的宽度怎么样去估算?

只要不routing能过,power straps 越多越好,这个得根据你的设计决定

有沒有 APR 教學類的書可參考?告訴大家跑多少 ma多寬?

還有還是說先 APR-> 跑 power drop .. 和RD 討論後覺得某些地方 POWER LINE 不夠在去補?

顶一下!

额,我也是今年4月才开始做后端,都是在这个论坛里看了些基础的资料,然后跑公司前辈的脚本,自己慢慢捉摸。所以。sorry啦!

期待,有没有软件帮忙解决。