ICC做完route之后,report_congestion发现有overflow,请问这个怎么解决呢?

Both Dirs: Overflow = 69 Max = 2 (5 GRCs) GRCs = 64 (0.77%)

H routing: Overflow = 30 Max = 2 (2 GRCs) GRCs = 28(0.34%)

V routing: Overflow = 39 Max = 2 (3 GRCs) GRCs = 36(0.43%)

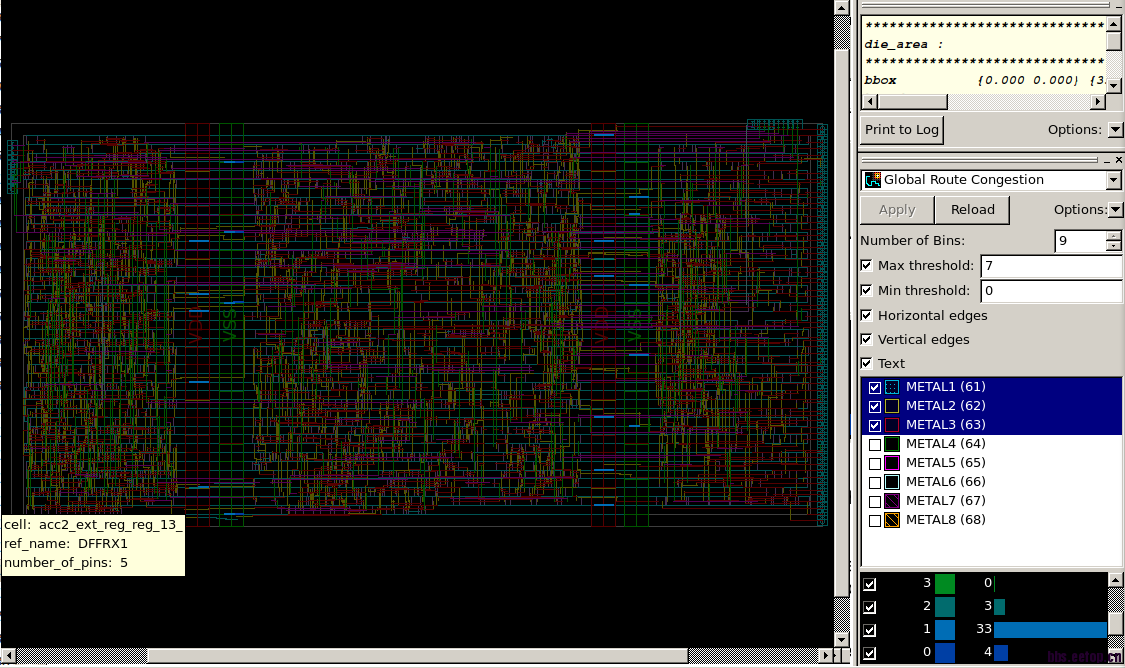

METAL1: Overflow = 20 Max = 1 (20 GRCs) GRCs = 20 (0.48%)

METAL2: Overflow = 39 Max = 2 (3 GRCs) GRCs = 36 (0.87%)

METAL3: Overflow = 10 Max = 2 (2 GRCs) GRCs = 8 (0.19%)

METAL4: Overflow = 0 Max = 0 (0 GRCs) GRCs = 0 (0.00%)

METAL5: Overflow = 0 Max = 0 (0 GRCs) GRCs = 0 (0.00%)

METAL6: Overflow = 0 Max = 0 (0 GRCs) GRCs = 0 (0.00%)

METAL7: Overflow = 0 Max = 0 (0 GRCs) GRCs = 0 (0.00%)

METAL8: Overflow = 0 Max = 0 (0 GRCs) GRCs = 0 (0.00%)

place的时候没有overflow,route之后就有。这个难道还要重新place吗?

下图是global route的图,看得到在前三层金属上有overflow

一般都会有的,若是没有,那说明你的面积太大了。

只要没有drc lvs错误就可以了

那意思是不是说,实际上市可以布线上去。但是因为这个report_congestion是通过global route来计算的,所以结果不是很准确。

这个问题还有没有人帮忙解释一下呀?ICC布线后计算的congestion怎么解决呢?

在Place阶段 set place_enable_enhace_router true

place_opt -congestion试试。

调整FloorPlan

试试

congestion number evaluation只在 route之前有意义,

因为route之前是用virutal route 的模型去估计的

一旦route后, 就看最后的drc number了,

verify_zrt_route 就知道了,

Total number of nets = 1346, of which 0 are not extracted

Total number of open nets = 0, of which 0 are frozen

Total number of excluded ports = 0 ports of 0 unplaced cells connected to 0 nets

0 ports without pins of 0 cells connected to 0 nets

0 ports of 0 cover cells connected to 0 non-pg nets

Total number of DRCs = 1066

Total number of antenna violations = 0

Total number of voltage-area violations = 0

这个报告是不是说我有1066个congestion?

对,没错, 用Error Browser 看下,

比较多了

哦,十分感谢你的耐心回答。但是我的core已经比较大了,std cell的utilization才35%。电源带占用面积也很小,但是不管我怎么优化总是会出现congestion。这种情况的话一般是怎么解决呢?是不是需要在floorplan的时候把core utilization提高呢?

这个很奇怪, utilization减小只会使得route变容易而不是变困难, 应该是0个violation,

最后route结束的时候utilization多少?

问下 violation在哪里,是power strap下面么, error browser看下, 截个图给大家看看,

你这不是1066个congestion。 是1066个DRCoverflow 并不能完全看成error, 只是说在某一段routing area 有比较多的线要走,所有会有些线off track,

但并不代表不能route, 只是比较有可能出现DRC error。

所以看一下overflow的比例和GRC的数量, 如果不大 是可以route的, after route 有DRC就手动修就是了

这个跟你的floorplan有关系的~ floorplan的好的话 不容易出congestion问题。 比方说 一些power strap下面

要尽量避免放std cell, 因为走线麻烦 要绕线。 还有IO多的macro或者cells 要尽量预留多点空间给pin routing

IO尽量走直线 避免直角~ 因为拐弯是很难地。要放via 又容易占地方又容易DRC

还有 floorplan 和 DP 的时候 加一些option 去constrain, 比如

set_preroute_drc_strategy-protect_pin_access_edge

set_pnet_options avoid placing std cells under p strap

set_fp_placement_strategy \

-congestion_effort high\

-legalizer_effort high\

-pin_routing_aware on

局部集中的std cells如果pin很多,会引起局部routing drc,可以尝试将这些std cells放散一些!

请问将stdcell放散一些,具体怎么操作?