做完CTS之后,clock tree的source insertion delay变成了负数是怎么回事

时间:10-02

整理:3721RD

点击:

hi 大家好:

最近在学习用innovus做clock tree,但是做完clock tree之后clock tree的source insertion delay变成了负数,是怎么回事?

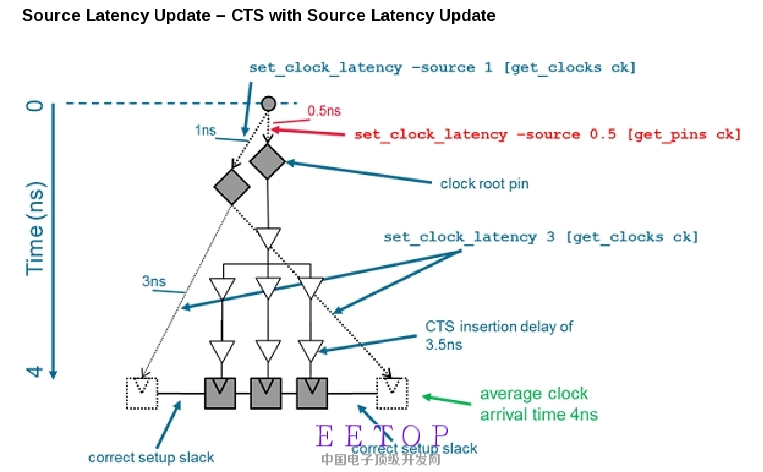

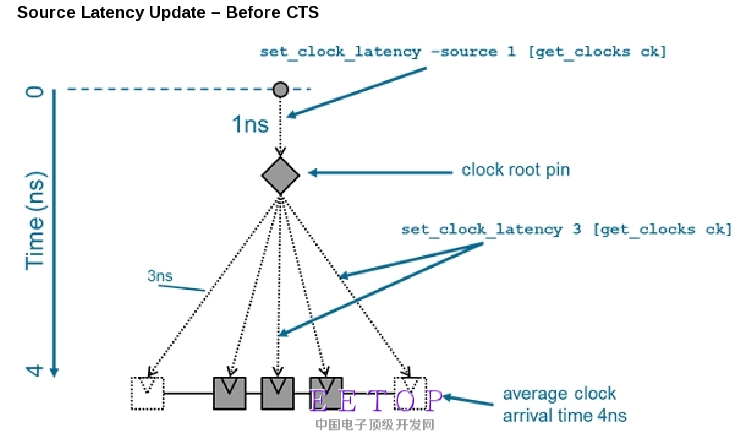

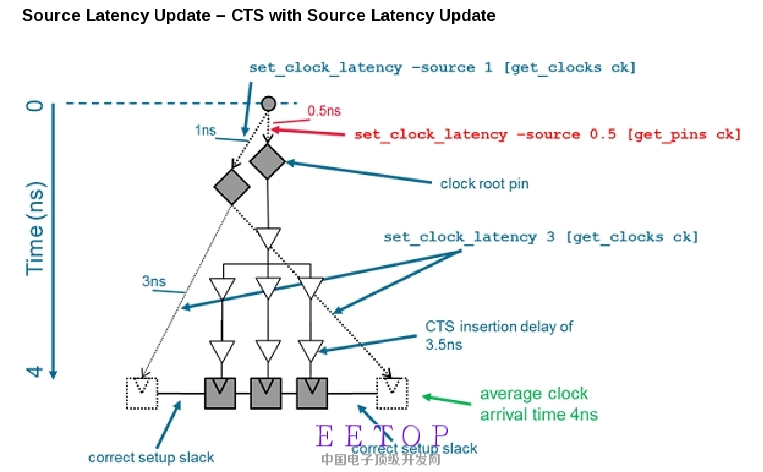

又看了一下user guide,上面说,为了保证post-cts跟pre-cts的IO path上的timing一致(in2reg、reg2out),工具会自动update IO latency,对应的属性为update_io_latency。

又看了一下user guide,上面说,为了保证post-cts跟pre-cts的IO path上的timing一致(in2reg、reg2out),工具会自动update IO latency,对应的属性为update_io_latency。

最近在学习用innovus做clock tree,但是做完clock tree之后clock tree的source insertion delay变成了负数,是怎么回事?

有可能是PLL Feedback引起,也有可能是ccopt前没设propagated clock工具自动加的clock latency

“也有可能是ccopt前没设propagated clock工具自动加的clock latency” 这句话怎么理解,ccopt之前clock 应该是ideal的才对,怎么理解?

又看了一下user guide,上面说,为了保证post-cts跟pre-cts的IO path上的timing一致(in2reg、reg2out),工具会自动update IO latency,对应的属性为update_io_latency。

又看了一下user guide,上面说,为了保证post-cts跟pre-cts的IO path上的timing一致(in2reg、reg2out),工具会自动update IO latency,对应的属性为update_io_latency。

个人感觉这个功能够奇葩的,还没有深入了解,不知道有什么用