分频时钟问题

时间:10-02

整理:3721RD

点击:

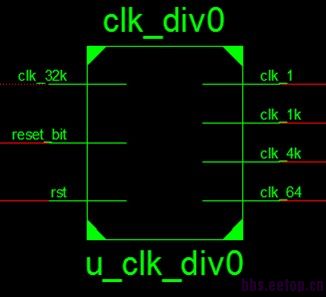

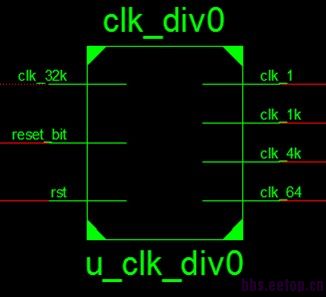

有下图所示的分频模块源时钟为clk_32k,产生clk_1,clk_1k,clk_4k,clk_64四个分频时钟,这四个时钟可作为之后其他模块的源时钟,请问定义此分频时钟时应该定义到分频产生的端点,还是后面的输入点,比如clk_1输入到TOP/A模块应该定义为set_generated_clock -source clk_32k -devided by 32768 [get_ports TOP/clk_div0/clk_1]还是set_generated_clock -source clk_32k -devided by 32768 [get_ports TOP/A/clk_1]?

TOP/clk_div0/clk_1

原则是越靠前越好

哦哦,谢谢小编,你那个FAQ中说要加一个BUF,然后在BUF输出的点定义分频时钟,加BUF有什么好处,是在哪个过程中插BUF呢?

在 FAQ里面有帖子的链接