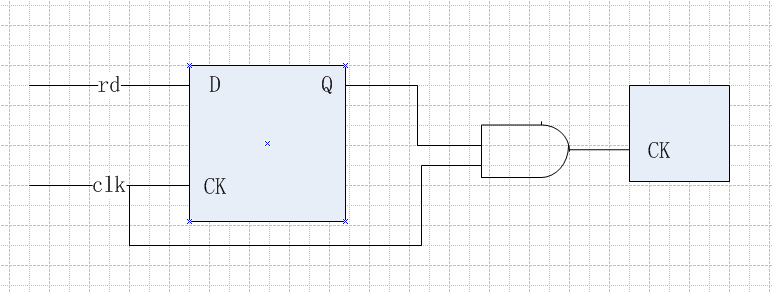

inputdelay在对如下电路的设置问题

时间:10-02

整理:3721RD

点击:

如图,外部信号rd,我在dc的约束里面没有设置input delay

clk的周期为59ns。

从input端rd到第一个dff,dc会报告一个保持时间违背。

报告如下,rd输入到dff的d端的时候会有一个(net 0.15ns)的延时,可能因为我给的rd的驱动是set_driving_cell buf/O。想问问要怎么处理set_input_delay?

Startpoint: rd (input port)

Endpoint: reg_array/clk_gate_data_out_reg_7/latch

(negative level-sensitive latch clocked by src_clk)

Path Group: src_clk

Path Type: min

Des/Clust/PortWire Load ModelLibrary

------------------------------------------------

ecpenG2000Kfs90a_c_generic_core_ss2p25v125c

PointFanoutCapTransIncrPath

----------------------------------------------------------------------------------------------

clock (input port clock) (rise edge)0.000.00

clock network delay (ideal)0.000.00

input external delay0.000.00 f

rd (in)0.280.150.15 f

rd (net)10.140.000.15 f

reg_array/rd (reg_array)0.000.15 f

reg_array/rd (net)0.140.000.15 f

reg_array/clk_gate_data_out_reg_7/EN (SNPS_CLOCK_GATE_HIGH_reg_array_1)0.000.15 f

reg_array/clk_gate_data_out_reg_7/EN (net)0.140.000.15 f

reg_array/clk_gate_data_out_reg_7/latch/D (QDBHN)0.280.000.15 f

data arrival time0.15

clock src_clk (rise edge)59.5259.52

clock network delay (ideal)0.0059.52

reg_array/clk_gate_data_out_reg_7/latch/CKB (QDBHN)0.0059.52 r

library hold time-0.1359.39

data required time59.39

----------------------------------------------------------------------------------------------

data required time59.39

data arrival time-0.15

----------------------------------------------------------------------------------------------

slack (VIOLATED)-59.24

补充一下,其实问题在于,为何data_require_time的检查要在59.52开始?如何设置到0ns开始?