hold 违例修不掉,怎么办?

时间:10-02

整理:3721RD

点击:

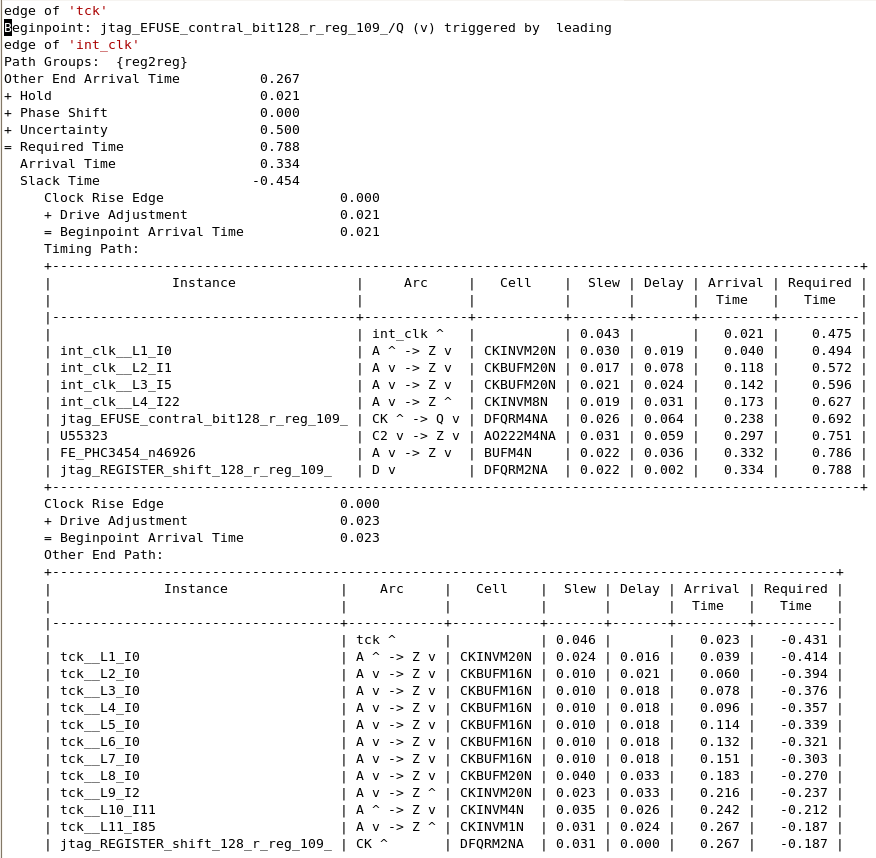

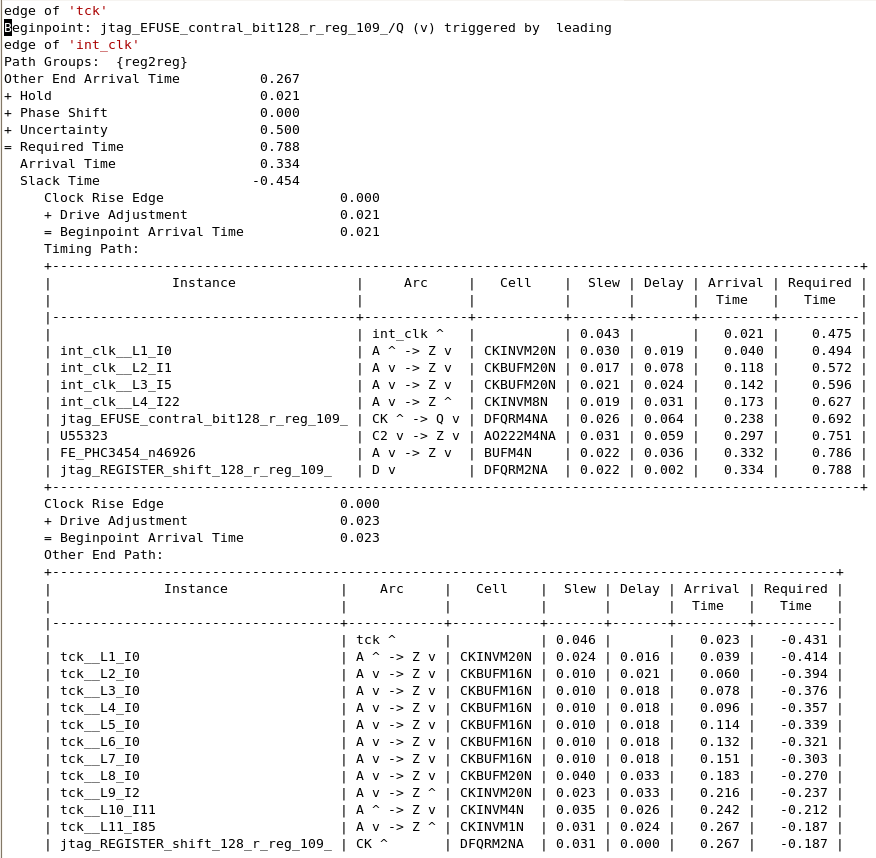

时序路径如图

现在是有几条这两个时钟之间的hold违例,始终优化不掉,请问该怎么解决呀?

现在是有几条这两个时钟之间的hold违例,始终优化不掉,请问该怎么解决呀?

uncertainty 0.5ns? 都已经是CTS之后了,这个值设得太大了吧?

CTS后,sdc中时钟的uncertainty一般设置多大呀?

CTS后,已经生成真实的时钟,这时重新导入的sdc中还需要在创建时钟吗?要创建的话,该怎么约束呀?

谢谢

这个得根据你整个芯片的预算来算吧

比如说你时钟从PLL出来以后,到底有多少延时

cts以后就是传播时钟模型了(Propagated Model)

这个要根据自己的设计以及目标来设置,uncertainty的设置会影响工具对时序的优化,怎么样设好,要分析

uncertainty在post route的时候可以适当小一点,特别是给hold的值更要小,而且,这个uncertainty不是随便估计的,要根据你的pll jitter和其他因素来考量。

你的两个时钟int_clk和clk是同一个时钟域的么?如果是异步时钟,在约束里面不是要加set_false_path?

想请教您:如何确认设计里的两个时钟是什么关系?而且sdc里面两个时钟都是用creat_clock创建的时钟,做时钟树是要分开做吗?(用的工具是ICC)谢谢!

如果是完全异步的时钟,就是毫无相位关系,那么是需要set_false_path的

而如果是毫无相位关系的时钟,CTS方面,应该是单独做,保证自己时钟域内的skew较小即可。

一般uncertainty的设置 signoff 是有标准的 。

后端最后的hold violation有可能需要手工修正