lvs的一个报错问题

最近在做一个lvs的练习,需要将两个ip连接起来,得到最后的芯片

其中一个ip名字为top,有spice网表,并且单独验证top的lvs没有问题,top的电源为VCC和GND

另外一个ip为eeprom,是foundry提供的硬核ip,没有rtl相关信息,

为了能够在edi中调用这两个ip,需要在rtl代码中定义一个eeprom和一个top的顶层,并只声明top和eeprom的接口信号(input/output),电源部分为VDD和GND、VCC和GND

并且eeprom和top的电源是分开供电的,两者都有自己的电源环,虽然两者可以供地,但在edi中没有将两者的地连接起来。

在完成最后一步拼接的时候,在edi中只做了route这一步

calibre部分:

总的spice网表为rfid(top+eeprom),并且在rfid的spice网表开头部分加上了INCLUDE“top.spi”,由于eeprom没有spice,在lvs规则文件后加上了lvs box eeprom ;lvs box source eeprom; lvs layout eeprom,也就是将eeprom做成黑盒子

1.同时在eeprom的接口上,加上了VDD和GND这两个pin,spice网表中声明GLOBAL VDD GND,在调用EEPROM的时候,在eeprom的端口上加上VDD=VDD GND=GND

在进行lvs后得到报告,结果为layout中eeprom有一个gnd,但是source部分由这样的gnd的错误;

猜测,为何仅仅只是gnd被报错,为何VDD没有报错?会不会是因为top和eeprom的地都是一样的名字,导致了calibre的错误?

如果没有1标注的这一步,虽然lvs会报错,但是没有说明是什么原因?通过calibre RVE没法高亮错误点。

求助,如何处理这样的情况?也就是在两个ip的情况下,如何处理其中一个没有spice网表的,但是有电源的ip?

不知所云,直接贴报告吧

你写了黑盒子网标了吗? 黑盒子也是要网表的,一个有端口信息的网表。

.SUBCKT eeprom_topportname1 portname2 ...

.END

rfid(top+eeprom),rfid 网表中加上

.includetop.spi

.includeeeprom_top.spi

你好,黑盒子部分的顶层端口网表写了,

但是foundry给的这个eeprom没有eeprom.spi,只是一个硬核,所以只能做接口上的检查。

你好,请问

在lvs rule的power name和ground name与在spice网表中的.global power_name ground_name之间是不是必须一样?两者有没有什么区别和联系?两者的作用又分别是什么?

我的问题最后得到的报告如下,可见,总的overall comparison result是通过的,但是有一个警告。

OVERALL COMPARISON RESULTS

####################

###**

###CORRECT#|

# ###\___/

####################

Warning:Components with non-identical power or ground pins.

**************************************************************************************************************

CELLSUMMARY

**************************************************************************************************************

ResultLayoutSource

------------------------------------

CORRECTAN2AN2

CORRECTAN2B1SAN2B1S

CORRECTAN2SAN2S

CORRECTAN3B1AN3B1

CORRECTAN3SAN3S

CORRECTAN4B1SAN4B1S

CORRECTAO112SAO112S

CORRECTAO12AO12

CORRECTAO13AO13

.......

CORRECTTIE0TIE0

CORRECTTIE1TIE1

CORRECTXNR2XNR2

CORRECTXOR2XOR2

CORRECTXOR2SXOR2S

CORRECTtoptop

CORRECTrfidrfid

**************************************************************************************************************

INFORMATION AND WARNINGS

**************************************************************************************************************

o Component types with non-identical power or ground pins:

(Cells with the same ( or corresponding ) name that have different voltage

pin names are listed below.Pins that do not appear in all corresponding

cells in both source and layout are ignored by the comparison algorithm.)

Layout Component Type:HJ250EEPEE8K1PL_E (38 pins)

Extra Pins:VDD GND

Source Component Type:HJ250EEPEE8K1PL_E (36 pins

你把HJ250EEPEE8K1PL_E 网表里加上 VDD GND两个PORT 还不行吗?

我太明白你说的加是只怎么个加法,我说说我的操作

首先HJ250EEPEE8K1PL_E,也就是eeprom是一个硬核ip,foundry没有给spi网表

eeprom的spice网表出现在两个第一方,一个是调用,一个是声明

你说的是在声明的时候加上VDD和GND?还是说在声明和调用的时候都加上?

不管是哪种方法,我都试过。在调用的时候加上电源时,还要写VDD=VDD GND=GND把这个端口对应上。

HJ250EEPEE8K1PL_E 模块的的网中加上VDD GND,就是3楼说的.SUBCKT eeprom_topportname1 portname2 ... VDD GND

.END

还有一种办法就是在版图上将VDD GND 该成 VDD!GND!,不过这样就可能有其他问题,要注意设置好选项,要不没有连接的VDD gnD 不会报出了

我懂你的意思,我按照这个规则已经设置了,就是在eeprom的端口上加上了VDD和GND,在调用eeprom的时候,还加上了VDD=VDD GND=GND,但是没有效果,还是有这个warning。我自己做的top部分,也是抽出lef,gds后,一样的办法做lvs,都可以过,而且没有加电源在portname上。我猜测这个可能是foundry的问题吧,或者是black box在电源上有些什么特别的设置。

如果你这个方法试过了的话,我想到还有一种情况,不知道是不是,你可以打开LAYOUT看看。

eeprom_toplayout VDD 和GND 用了两层或两层以上的金属,而这两层金属没有用VIA连接起来,又或者有两个或两个以上的地方有写VDD GND名字,可能会出现你这个情况。

RUN LVS-H 情况是加上 LVS REPORT OPTION X, 可看见详细的REPORT。

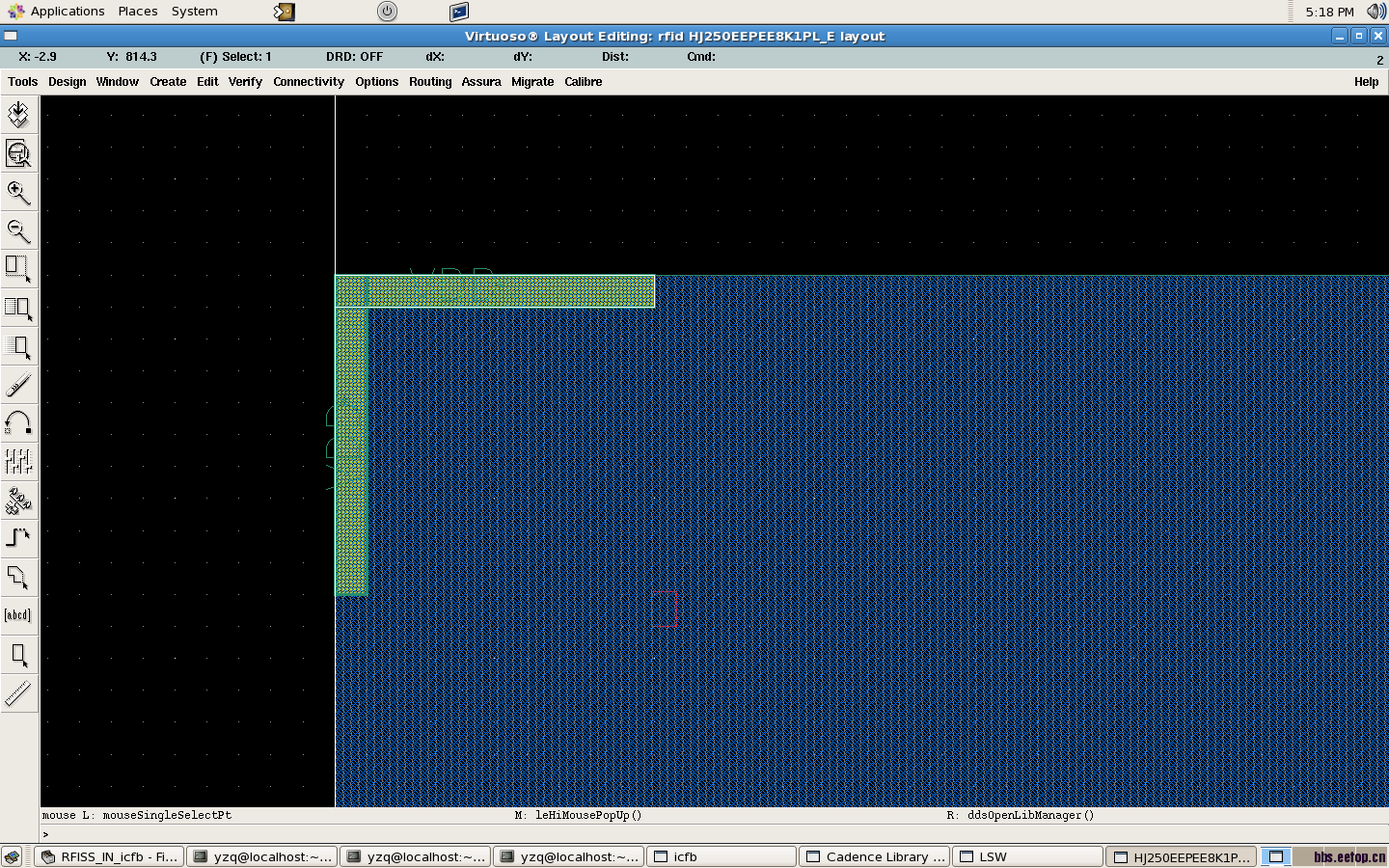

你好,你说的eeprom可能有两个VDD和GND的情况我已经检查过了,图片如下

我曾经做过一个尝试,如果将VDD和GND,与top部分的电源和地连接在一起(我指的是APR时),那么lvs就不会报这个警告

eeprom的GND情况

如果不涉及太大问题的话(只是个人练习用的数据),把网表发出来看看

学习中~

前来学习,高人多

你工作很认真,值得我们学习。

你还可以试试, 在LVS RULE里加上一句, VIRTUAL CONNECT NAME “VDD” “GND”,RUN一下试试。

如果还有WARNING的话,就打开EEPROM_TOP的LAYOUT,把里面所有的VDD/GND替换成VDD:/GND:,

然后在LVS RULE里加一句,

VIRTUAL CONNECT COLON YES

VIRTUAL CONNECT NAME “VDD" “GND”

原因是因为你的LAYOUT里有相同的名字而没有把它连接在一起导致。

你好,我已经按照你的意思在lvs rule中加上了如下句子VIRTUAL CONNECT NAME ?VDD? ?GND?

但是仍然没有效果,还是存在同样警告。

请问VIRTUAL CONNECT NAME 这个设置的意思是什么?是说VDD GND这样的电源是虚拟连接?也就是悬空的吗?

你提到的在eeprom的layout中进行修改,由于这个eeprom是硬核,所以没办法在icfb中选中这个label进行修改,只能说多打一个label,然后再把两个label在spice网表中用connect来连接起来。我的设计中也可以保证没有使用VDD的电源名,但是top部分的地名字和eeprom的地名字都是GND,只是说两个的电源没有连接起来。

还有就是这个eeprom是硬核,我想应该不会有什么问题,毕竟是foundry提供的。它lef中定义的电源和地如下:

PIN VDD

DIRECTION INOUT ;

USE POWER ;

SHAPE ABUTMENT ;

PORT

LAYER metal3 ;

RECT 0.000 802.000 1.000 812.000 ;

END

PORT

LAYER metal3 ;

RECT 0.000 811.000 10.000 812.000 ;

END

END VDD

PIN GND

DIRECTION INOUT ;

USE GROUND ;

SHAPE ABUTMENT ;

PORT

LAYER metal3 ;

RECT 452.240 811.000 462.240 812.000 ;

END

END GND

网表内容如下,由于eeprom没有spice网表,所以只能加个自己写的顶层,top.spi就是我抽出来的一个单独的lef对应的部分。

.INCLUDE "top.spi"

.SUBCKT HJ250EEPEE8K1PL_E Dout A[12] A[11] A[10] A[9] A[8] A[7] A[6] A[5] A[4]

+ A[3] A[2] A[1] A[0] Din CE_B OE_B WE_B WRITE ERASE WERASE ID_MODEB POR EECLK

+ EMOD[1] EMOD[0] CURENB SEL CELL_I[7] CELL_I[6] CELL_I[5] CELL_I[4] CELL_I[3]

+ CELL_I[2] CELL_I[1] CELL_I[0]

.ENDS

.SUBCKT rfid CLK CLR DATA_IN_ANA Trng_Data SEND_FINAL_OUT Trng_En

Xdigit top $PINS clk=CLK rst_b=CLR data_in_ana=DATA_IN_ANA

+ rand_data_out=Trng_Data send_final_out=SEND_FINAL_OUT rand_en=Trng_En dout=dout

+ a[12]=a[12] a[11]=a[11] a[10]=a[10] a[9]=a[9] a[8]=a[8] a[7]=a[7] a[6]=a[6]

+ a[5]=a[5] a[4]=a[4] a[3]=a[3] a[2]=a[2] a[1]=a[1] a[0]=a[0] din=din por=por

+ ce_b=ce_b oe_b=oe_b we_b=we_b id_modeb=id_modeb curenb=curenb emod[1]=emod[1]

+ emod[0]=emod[0] werase=werase erase=erase write=write eeclk=eeclk sel=sel

+ cell_i[7]=cell_i[7] cell_i[6]=cell_i[6] cell_i[5]=cell_i[5] cell_i[4]=cell_i[4]

+ cell_i[3]=cell_i[3] cell_i[2]=cell_i[2] cell_i[1]=cell_i[1] cell_i[0]=cell_i[0]

Xeeprom HJ250EEPEE8K1PL_E $PINS Dout=dout A[12]=a[12] A[11]=a[11] A[10]=a[10]

+ A[9]=a[9] A[8]=a[8] A[7]=a[7] A[6]=a[6] A[5]=a[5] A[4]=a[4] A[3]=a[3] A[2]=a[2]

+ A[1]=a[1] A[0]=a[0] Din=din CE_B=ce_b OE_B=oe_b WE_B=we_b WRITE=write

+ ERASE=erase WERASE=werase ID_MODEB=id_modeb POR=por EECLK=eeclk EMOD[1]=emod[1]

+ EMOD[0]=emod[0] CURENB=curenb SEL=sel CELL_I[7]=cell_i[7] CELL_I[6]=cell_i[6]

+ CELL_I[5]=cell_i[5] CELL_I[4]=cell_i[4] CELL_I[3]=cell_i[3] CELL_I[2]=cell_i[2]

+ CELL_I[1]=cell_i[1] CELL_I[0]=cell_i[0]

.ENDS

.GLOBAL VDD GND

top.spi的内容是什么?

下面这一部分么?

.SUBCKT top ……………………

cell 名称为top吧?

对应整体里是digit?

你试试用我这样改的网表怎么样,添加加粗的地方

.SUBCKT rfid VDD VCC

Xeeprom HJ250EEPEE8K1PL_E $PINS inh_vdd=VCC

Xdigit top $PINS inh_vdd=VDD

.SUBCKT HJ250EEPEE8K1PL_E inh_vdd

.SUBCKT top inh_vdd

.GLOBALGND

整个结构是这样的:rfid=top+eeprom;top部分就是一个自己单独拿出来先走一遍流程的,电源为VCC和GND ,top.spi就是这个流程得到的一个spice网表,然后在第二次流程时候,加上的rfid=top+eeprom,所以在rfid的网表里面需要加上include"top.spi"。

小编说的这个inh是?

还有就是小编的电源是不是弄错了,eeprom的是VDD,top的才是VCC,是不是要修改下你的这个网表?

eeprom的是VDD,top的才是VCC

就按你说的办

我反正知道你两个不一样

如果你不在网表中指定,那么你即便GLOBAL,它自己是无法知道谁应该接到谁上的

网表修改内容如下,注意红色为修改部分。

.SUBCKT HJ250EEPEE8K1PL_E Dout A[12] A[11] A[10] A[9] A[8] A[7] A[6] A[5] A[4]

+ A[3] A[2] A[1] A[0] Din CE_B OE_B WE_B WRITE ERASE WERASE ID_MODEB POR EECLK

+ EMOD[1] EMOD[0] CURENB SEL CELL_I[7] CELL_I[6] CELL_I[5] CELL_I[4] CELL_I[3]

+ CELL_I[2] CELL_I[1] CELL_I[0] inh_vdd

.ENDS

.SUBCKT rfid CLK CLR DATA_IN_ANA Trng_Data SEND_FINAL_OUT Trng_En VDD VCC

Xdigit top $PINS clk=CLK rst_b=CLR data_in_ana=DATA_IN_ANA

+ rand_data_out=Trng_Data send_final_out=SEND_FINAL_OUT rand_en=Trng_En dout=dout

+ a[12]=a[12] a[11]=a[11] a[10]=a[10] a[9]=a[9] a[8]=a[8] a[7]=a[7] a[6]=a[6]

+ a[5]=a[5] a[4]=a[4] a[3]=a[3] a[2]=a[2] a[1]=a[1] a[0]=a[0] din=din por=por

+ ce_b=ce_b oe_b=oe_b we_b=we_b id_modeb=id_modeb curenb=curenb emod[1]=emod[1]

+ emod[0]=emod[0] werase=werase erase=erase write=write eeclk=eeclk sel=sel

+ cell_i[7]=cell_i[7] cell_i[6]=cell_i[6] cell_i[5]=cell_i[5] cell_i[4]=cell_i[4]

+ cell_i[3]=cell_i[3] cell_i[2]=cell_i[2] cell_i[1]=cell_i[1] cell_i[0]=cell_i[0]

+ inh_vdd=VCC

Xeeprom HJ250EEPEE8K1PL_E $PINS Dout=dout A[12]=a[12] A[11]=a[11] A[10]=a[10]

+ A[9]=a[9] A[8]=a[8] A[7]=a[7] A[6]=a[6] A[5]=a[5] A[4]=a[4] A[3]=a[3] A[2]=a[2]

+ A[1]=a[1] A[0]=a[0] Din=din CE_B=ce_b OE_B=oe_b WE_B=we_b WRITE=write

+ ERASE=erase WERASE=werase ID_MODEB=id_modeb POR=por EECLK=eeclk EMOD[1]=emod[1]

+ EMOD[0]=emod[0] CURENB=curenb SEL=sel CELL_I[7]=cell_i[7] CELL_I[6]=cell_i[6]

+ CELL_I[5]=cell_i[5] CELL_I[4]=cell_i[4] CELL_I[3]=cell_i[3] CELL_I[2]=cell_i[2]

+ CELL_I[1]=cell_i[1] CELL_I[0]=cell_i[0] inh_vdd=VDD

.ENDS

.SUBCKT top clk rst_b data_in_ana send_final_out rand_en rand_data_out dout

+ a[12] a[11] a[10] a[9] a[8] a[7] a[6] a[5] a[4] a[3] a[2] a[1] a[0] din por

+ ce_b oe_b we_b id_modeb curenb emod[1] emod[0] werase erase write eeclk sel

+ cell_i[7] cell_i[6] cell_i[5] cell_i[4] cell_i[3] cell_i[2] cell_i[1]

+ cell_i[0] inh_vdd

...............

.ENDS

.GLOBAL GND

我不太赞成这样的网表修改方法,这就好像在网表中多增加了extra pins:inh_vdd,但是版图部分是不能识别到这个inh_vdd。

修改后的网表进行lvs得到错误报告如下:

红色部分为与之前报告的区别,从区别处来看,lvs过程时,对source部分的eeprom,认为source部分多了一个extra pins inh_vdd。从最后的warning部分的source eeprom也可以看出来eeprom source 部分多了一个pins,之前是36个pins

**************************************************************************************************************

COMPONENT TYPES WITH NON-IDENTICAL SIGNAL PINS

**************************************************************************************************************

OVERALL COMPARISON RESULTS

#######################

# ###

##INCORRECT#

# ###

#######################

Error:Components with non-identical signal pins.

Warning:Components with non-identical power or ground pins.

(Cells with the same ( or corresponding ) name that have different signal

pin names are listed below.Pins that do not appear in all corresponding

cells in both source and layout are ignored by the comparison algorithm.)

Layout Component Type:HJ250EEPEE8K1PL_E (38 pins)

No Extra Pins.

Layout Instances:

Cell:rfid

Instances:X1(5.000,757.090)

Source Component Type:HJ250EEPEE8K1PL_E (37 pins)

Source Extra Pins:inh_vdd

Source Instances:

Cell:rfid

Instances:Xeeprom

Result Component Type:HJ250EEPEE8K1PL_E (36 pins)

**************************************************************************************************************

INFORMATION AND WARNINGS

**************************************************************************************************************

o Component types with non-identical power or ground pins:

(Cells with the same ( or corresponding ) name that have different voltage

pin names are listed below.Pins that do not appear in all corresponding

cells in both source and layout are ignored by the comparison algorithm.)

Layout Component Type:HJ250EEPEE8K1PL_E (38 pins)

Extra Pins:VDD GND

Source Component Type:HJ250EEPEE8K1PL_E (37 pins)

estyzq 说:修改后的网表进行lvs得到错误报告如下:红色部分为与之前报告的区别,从区别处来看,lvs过程时,对source ...

为啥帖子里看不到?只在提醒里面看到了

修改后的网表进行lvs得到错误报告如下:

红色部分为与之前报告的区别,从区别处来看,lvs过程时,对source部分的eeprom,认为source部分多了一个extra pins inh_vdd。从最后的warning部分的source eeprom也可以看出来eeprom source 部分多了一个pins,之前是36个pins

**************************************************************************************************************

COMPONENT TYPES WITH NON-IDENTICAL SIGNAL PINS

**************************************************************************************************************

OVERALL COMPARISON RESULTS

#######################

# ###

##INCORRECT#

# ###

#######################

Error:Components with non-identical signal pins.

Warning:Components with non-identical power or ground pins.

(Cells with the same ( or corresponding ) name that have different signal

pin names are listed below.Pins that do not appear in all corresponding

cells in both source and layout are ignored by the comparison algorithm.)

Layout Component Type:HJ250EEPEE8K1PL_E (38 pins)

No Extra Pins.

Layout Instances:

Cell:rfid

Instances:X1(5.000,757.090)

Source Component Type:HJ250EEPEE8K1PL_E (37 pins)

Source Extra Pins:inh_vdd

Source Instances:

Cell:rfid

Instances:Xeeprom

Result Component Type:HJ250EEPEE8K1PL_E (36 pins)

**************************************************************************************************************

INFORMATION AND WARNINGS

**************************************************************************************************************

o Component types with non-identical power or ground pins:

(Cells with the same ( or corresponding ) name that have different voltage

pin names are listed below.Pins that do not appear in all corresponding

cells in both source and layout are ignored by the comparison algorithm.)

Layout Component Type:HJ250EEPEE8K1PL_E (38 pins)

Extra Pins:VDD GND

Source Component Type:HJ250EEPEE8K1PL_E (37 pins)

.GLOBAL GND VCC VDD也加上,用hier的模式跑,那个lvs report上来

加上.GLOBAL VDD GND VCC也不行

lvs.rep报告如下:

##################################################

####

##C A L I B R ES Y S T E M##

####

##L V SR E P O R T##

####

##################################################

REPORT FILE NAME:lvs.rep

LAYOUT NAME:svdb/rfid.sp ('rfid')

SOURCE NAME:./data/rfid.spi ('rfid')

RULE FILE:LVS-L9-002-1P5M-CALIBRE-2.2-P12.txt

RULE FILE TITLE:HJTC 0.25um 2.5V/3.3V 1P5M LOGIC Process

HCELL FILE:(-automatch)

CREATION TIME:Fri Mar2 16:28:01 2012

CURRENT DIRECTORY:/home/yzq/workspace/projects/rfiss_in_lvs

USER NAME:yzq

CALIBRE VERSION:v2009.1_35.24Fri Apr 3 15:10:02 PDT 2009

OVERALL COMPARISON RESULTS

#######################

# ###

##INCORRECT#

# ###

#######################

Error:Components with non-identical signal pins.

Warning:Components with non-identical power or ground pins.

**************************************************************************************************************

CELLSUMMARY

**************************************************************************************************************

ResultLayoutSource

------------------------------------

CORRECTAN2AN2

CORRECTAN2B1SAN2B1S

CORRECTAN2SAN2S

CORRECTAN3B1AN3B1

CORRECTAN3SAN3S

CORRECTAN4B1SAN4B1S

.......

CORRECTTIE0TIE0

CORRECTTIE1TIE1

CORRECTXNR2XNR2

CORRECTXOR2XOR2

CORRECTXOR2SXOR2S

CORRECTtoptop

CORRECTrfidrfid

**************************************************************************************************************

LVS PARAMETERS

**************************************************************************************************************

o LVS Setup:

// LVS COMPONENT TYPE PROPERTY

// LVS COMPONENT SUBTYPE PROPERTY

// LVS PIN NAME PROPERTY

LVS POWER NAME"?VDD?" "?VCC?"

LVS GROUND NAME"?GND?" "?VSS?"

LVS CELL SUPPLYNO

LVS RECOGNIZE GATESNONE

LVS IGNORE PORTSNO

LVS CHECK PORT NAMESNO

LVS IGNORE TRIVIAL NAMED PORTSNO

LVS BUILTIN DEVICE PIN SWAPYES

LVS ALL CAPACITOR PINS SWAPPABLENO

LVS DISCARD PINS BY DEVICENO

LVS SOFT SUBSTRATE PINSNO

LVS INJECT LOGICYES

LVS EXPAND UNBALANCED CELLSYES

LVS EXPAND SEED PROMOTIONSNO

LVS PRESERVE PARAMETERIZED CELLSNO

LVS GLOBALS ARE PORTSYES

LVS REVERSE WLNO

LVS SPICE PREFER PINSNO

LVS SPICE SLASH IS SPACEYES

LVS SPICE ALLOW FLOATING PINSYES

// LVS SPICE ALLOW INLINE PARAMETERS

LVS SPICE ALLOW UNQUOTED STRINGSNO

LVS SPICE CONDITIONAL LDDNO

LVS SPICE CULL PRIMITIVE SUBCIRCUITSNO

LVS SPICE IMPLIED MOS AREANO

// LVS SPICE MULTIPLIER NAME

LVS SPICE OVERRIDE GLOBALSNO

LVS SPICE REDEFINE PARAMNO

LVS SPICE REPLICATE DEVICESNO

LVS SPICE SCALE X PARAMETERSNO

LVS SPICE STRICT WLNO

// LVS SPICE OPTION

LVS STRICT SUBTYPESNO

LVS EXACT SUBTYPESNO

LAYOUT CASEYES

SOURCE CASEYES

LVS COMPARE CASENAMES TYPES SUBTYPES VALUES

LVS DOWNCASE DEVICENO

LVS REPORT MAXIMUM1000

LVS PROPERTY RESOLUTION MAXIMUM32

// LVS SIGNATURE MAXIMUM

// LVS FILTER UNUSED OPTION

LVS REPORT OPTIONA B C D S X

LVS REPORT UNITSYES

// LVS NON USER NAME PORT

// LVS NON USER NAME NET

// LVS NON USER NAME INSTANCE

// Reduction

LVS REDUCE SERIES MOSNO

LVS REDUCE PARALLEL MOSYES

LVS REDUCE SEMI SERIES MOSNO

LVS REDUCE SPLIT GATESYES

LVS REDUCE PARALLEL BIPOLARYES

LVS REDUCE SERIES CAPACITORSYES

LVS REDUCE PARALLEL CAPACITORSYES

LVS REDUCE SERIES RESISTORSYES

LVS REDUCE PARALLEL RESISTORSYES

LVS REDUCE PARALLEL DIODESYES

LVS REDUCTION PRIORITYPARALLEL

// Trace Property

TRACE PROPERTYmn(N_25)l l 3

TRACE PROPERTYmn(N_25)w w 3

TRACE PROPERTYmp(P_25)l l 3

TRACE PROPERTYmp(P_25)w w 3

TRACE PROPERTYmn(N_33)l l 3

TRACE PROPERTYmn(N_33)w w 3

TRACE PROPERTYmp(P_33)l l 3

TRACE PROPERTYmp(P_33)w w 3

TRACE PROPERTYmn(NB)l l 3

TRACE PROPERTYmn(NB)w w 3

TRACE PROPERTYmp(PB)l l 3

TRACE PROPERTYmp(PB)w w 3

TRACE PROPERTYr(RSNWELL)r r 3

TRACE PROPERTYr(RSND)r r 3

TRACE PROPERTYr(RSPD)r r 3

TRACE PROPERTYr(RSNPO)r r 3

TRACE PROPERTYr(RNND)r r 3

TRACE PROPERTYr(RNPD)r r 3

TRACE PROPERTYr(RNNPO)r r 3

TRACE PROPERTYr(RNPPO)r r 3

TRACE PROPERTYda a 3

TRACE PROPERTYdp p 3

TRACE PROPERTYq(PNP_V100X100)a a 3

TRACE PROPERTYq(PNP_V200X200)a a 3

**************************************************************************************************************

COMPONENT TYPES WITH NON-IDENTICAL SIGNAL PINS

**************************************************************************************************************

(Cells with the same ( or corresponding ) name that have different signal

pin names are listed below.Pins that do not appear in all corresponding

cells in both source and layout are ignored by the comparison algorithm.)

Layout Component Type:HJ250EEPEE8K1PL_E (38 pins)

No Extra Pins.

Layout Instances:

Cell:rfid

Instances:X1(5.000,757.090)

Source Component Type:HJ250EEPEE8K1PL_E (37 pins)

Source Extra Pins:inh_vdd

Source Instances:

Cell:rfid

Instances:Xeeprom

Result Component Type:HJ250EEPEE8K1PL_E (36 pins)

**************************************************************************************************************

INFORMATION AND WARNINGS

**************************************************************************************************************

o Component types with non-identical power or ground pins:

(Cells with the same ( or corresponding ) name that have different voltage

pin names are listed below.Pins that do not appear in all corresponding

cells in both source and layout are ignored by the comparison algorithm.)

Layout Component Type:HJ250EEPEE8K1PL_E (38 pins)

Extra Pins:VDD GND

Source Component Type:HJ250EEPEE8K1PL_E (37 pins)

奇了怪了,提醒里面有,怎么到这帖子里面就看不到了呢?

刷出来了,真奇怪