问一个encounter的hold检查问题

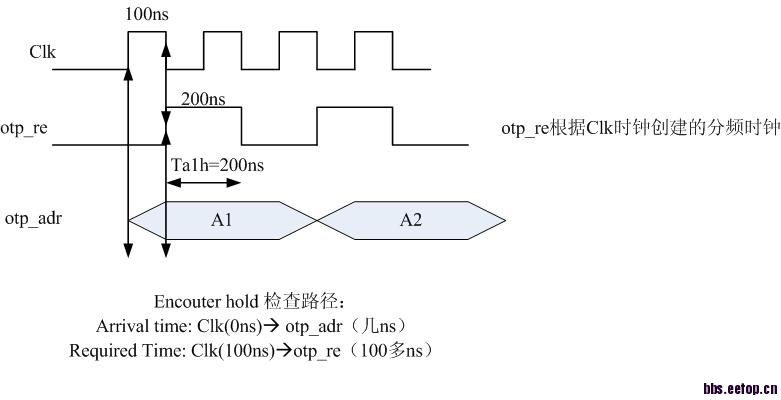

上面的图中的clk周期为200ns,otp_re周期为400ns,且otp_re和clk分别创建了时间,otp_re为clk的分频时钟

问题出现在otp_re和otp_adr的hold检查中,lib文件中要求otp_adr在otp_re的上升沿后保持200ns,设计中也注意

到这点,从上面可以看出,时序上市满足要求的

但是在encounter进行hold检查时,图中的Arrival time 比Required time少了100多ns,这样就照成Arrival time路径上插入很多不需要的delay单元,问一下这边该如何处理一下,谢谢!

这不是很正常啊, 保证200ns的hold margin,这个要求相当高了, 当然要插入很多delay cell了,

你看下到 otp_adr的timing path长否,

没关系的, 只要看edi的timing report, 用了正确的otp的 lib 值就行,是200ns对吧,

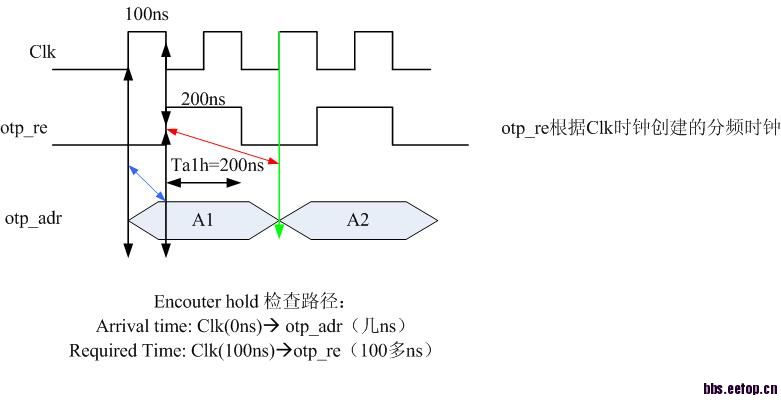

恩,楼上说的是对的,encounter检查了最紧的情况,也就是图中蓝色的箭头部分的hold,此时插入了很多单元(但是不是设计中想要的)

但是这不是设计中想要的,设计中只要保证otp_re上升沿以后otp_adr保持200ns不变就好了,我设计中是保证这样的时序要求的,也就是说我要让工具检查图中红色箭头的hold就可以了,这该如何操作了?

按理说不会啊, 如果 otp_adr 是针对 opt_re clock的来做hold check的话,

现在是对clk 来做了,确实是不对的,

这个path应设为false吧, 也就是只对 opt_reclock来做检查就行了

问题出现在两个时钟里面,otp_adr是根据clk时钟发生变化的,跟otp_re无直接关系,但是otp的lib文件要求otp_adr要满足otp_re上升沿以后要保持200ns

如果我要设置clk与otp_re的false path的话,那也就无法检查otp_adr要满足otp_re上升沿以后要保持200ns的时序要求了?如果工具只分析道图中红色部分的hold的话,就是我需要的了

不是设false path

因为master clock和its generated clock本身肯定不是false pth的,

你是定义 create_generated_clock -sourceclk-nameotp_re-divide_by 2这种么

对,是这样设置的,不过是Clk下沿来分频,不知道该如何屏蔽掉该路径?

对,是这样设置的,不知道该如何屏蔽掉该路径?

set_false_path -from CLK -to otp_adr 不行吗?

不太明白设置 set_false_path -from CLK -to otp_adr 的作用?

otp_adr的变化就是靠CLK上升沿来变化的,如果他们之间设置了false path的话,那otp_adr对于CLK的时序检查不就是没有了?

otp_re也是有CLK来产生的,为了满足otp_re和otp_adr之间的时序,设计上根据CLK的个数让他们之间交错开的,如果我不设置otp_re为CLK的分频时钟,encounter该如何检查otp_re和otp_adr之间的200ns的hold时序了?

试试set_false_path -hold -from CLK -to otp_adr