为什么电源电压下降,会导致门延迟增加?

时间:10-02

整理:3721RD

点击:

CMOS门的 动态功耗 正比于 VDD的平方,所以,降低VDD,可以降低动态功耗。

然而,降低VDD,会使gate delay 增加,请问这是为什么?求高手!

是VDD降低,对电容的充电变慢导致gate delay 增加了吗?

然而,降低VDD,会使gate delay 增加,请问这是为什么?求高手!

是VDD降低,对电容的充电变慢导致gate delay 增加了吗?

i = Q/t =CU/t ,

电压下降,电流就减少啊,电流减少器件就变慢啊,

看看别的理论公式,这个不一定准

i = Q/t = CU/t

电压下降,导致电流减小, 电流减小就是器件变慢啊

反过来,加压肯定变快啊,比如超频,

看看有没有别的更细致的理论公式

i = Q/T = CU/T ,

电压下降导致电流减小 ,电流减小也就是器件变慢啊

看看别的细致的理论公式

Rds会随电压降低而变大,而VTH一般不变,(即门翻转的电平没有变)

i = CU/T ,电压下降,导致电流下降,也就是器件变慢啊

要看看更加理论的公式就知道了

器件物理里面

受教。原来我把有一个概念和这个搞反了。

这个跟降低电压,transition变大有点相似吧

汽车没油不启动!

这跟i=Q/t 公式是没有关系的

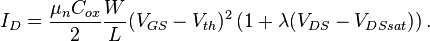

下面这个才是mosfet的电流公式

Vg - Vth 越大 电流自然也越大, saturation 状态下

有道理,还是微电子理论不行啊,

因为电压越大,输出电流越大,在充电电荷量不变的情况下,电流打了,对输出电容的充电越快。这样的话传输速度就会增大

门控电压和源电压是两回事~ 电源电压这里指门控电压不知道你所谓的 电压越大 电流越大 是指哪个电压 和哪个电流

Vdd,非Vgs