各位大虾帮忙分析一下LVS结果

时间:10-02

整理:3721RD

点击:

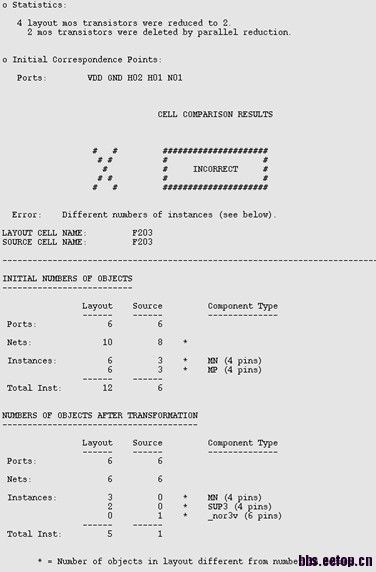

刚学着做LVS,跑完的时候report里有几个类似这样的错,请各位大虾帮忙分析一下里面的错误,比如说layout 和 source的instances下的MN,SUP3,_nor3v数量不一样,这是什么错误,不胜感激啦!

是不是你做LVS的电路所对应的层跟版图没对上,或者是你电路中调用的管子有问题,看下电路中的管子的模型名对不对

检查下连线。

我知道layout 和 source的net数量不一样可能是连线出现open了,但是instances下面的几个不一样是什么问题?

可能是端口连接错误的问题,造成了不匹配。具体你要自己检查版图。

我说的不匹配是器件的连接不匹配。

打个比方吧,你的意思是说本来A是和B相连的,但是错连到C上面去了,这样造成了不匹配对吧?

嗯,具体问题我也要检查版图才知道哈,这样说也不一定正确。

十有八九是线连错了阿

rule文件中R提取模式是否用的不对? 还有,内部net的short也会造成instance不匹配!

Rule文件是foundry提供的,怎么看R提取的对不对呢?另外LVS结果中全都是要么是layout报*not similar*,要么是source报*not similar*,所以应该不是short,short一般是layout的net比layout的少啊。

具體來說可能是連錯線...

不過還是要看layout才知道

我就看看 学学

很多可能,线连错可能性大