求助,数字IC设计后端的验证问题

时间:10-02

整理:3721RD

点击:

目前绘制出了版图完成了LVS,使用calibre提取了寄生参数

那么要怎么证明我的电路在有寄生参数的情况下依然可以正常工作?

是对版图和DC综合出的网标进行形式化验证吗?

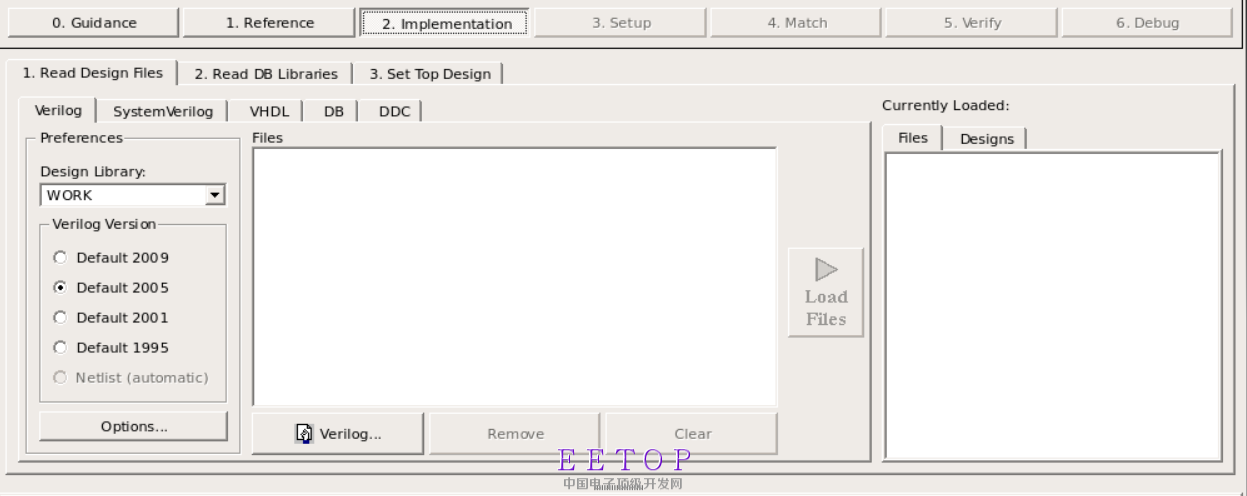

形式化验证可以输入两个版图进行比较吗?(我在gui界面没有看到可以输入ICC输出的GDSII文件的格式)如下图:

还是说,本身在对版图的LVS验证中已经完成对于带有寄生参数的电路的逻辑一致验证?

没有发出来的图

那么要怎么证明我的电路在有寄生参数的情况下依然可以正常工作?

是对版图和DC综合出的网标进行形式化验证吗?

形式化验证可以输入两个版图进行比较吗?(我在gui界面没有看到可以输入ICC输出的GDSII文件的格式)如下图:

还是说,本身在对版图的LVS验证中已经完成对于带有寄生参数的电路的逻辑一致验证?

没有发出来的图

形式验证需要用formal,比较的是优化前和优化后netlist功能是不是一致。LVS只是对比同一个database的layout和schematic(netlist)是不是一直而已。

我有点明白了

也就是说我现在只是验证了综合出来版图在逻辑方面与原本的设计是一致的

那么我应该怎么验证在考虑寄生参数的情况下,电路是可以正常工作的?

将你做好pr的设计抽取rc参数给其他做验证的人员做后仿,去验证带寄生参数电路功能正不正常

我也想啊= =

只是在片内集成的一小块spi

也没有别人做了只好自己来了

查了一天资料有一点想法写在这里,算是抛砖引玉吧

一个最终提交制造的版图应该满足:

功能和RTL一致

性能满足预定目标

物理规则正确

功耗&面积满足要求

那么,在signoff阶段

形式化验证是确定功能的

STA则是验证性能的

LVS,DRC验证的是物理规则

面积和功耗的报告是对于电路测试结果的一个验证

不知道这么理解有没有问题