cadence多层板via drc求助

时间:10-02

整理:3721RD

点击:

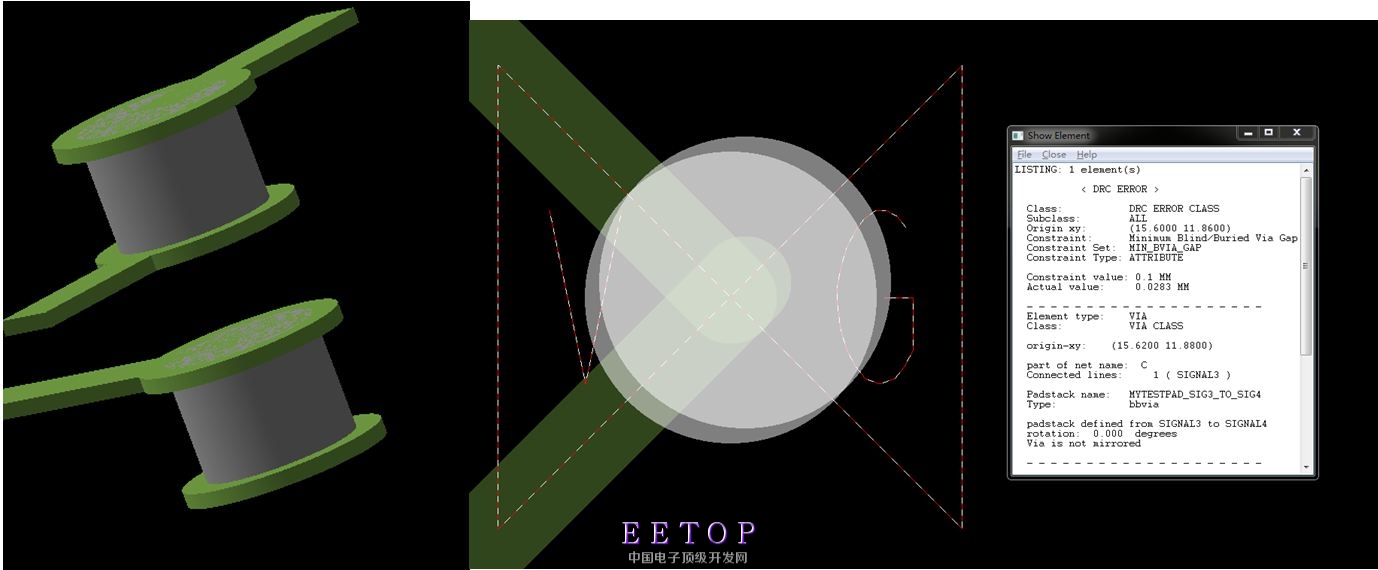

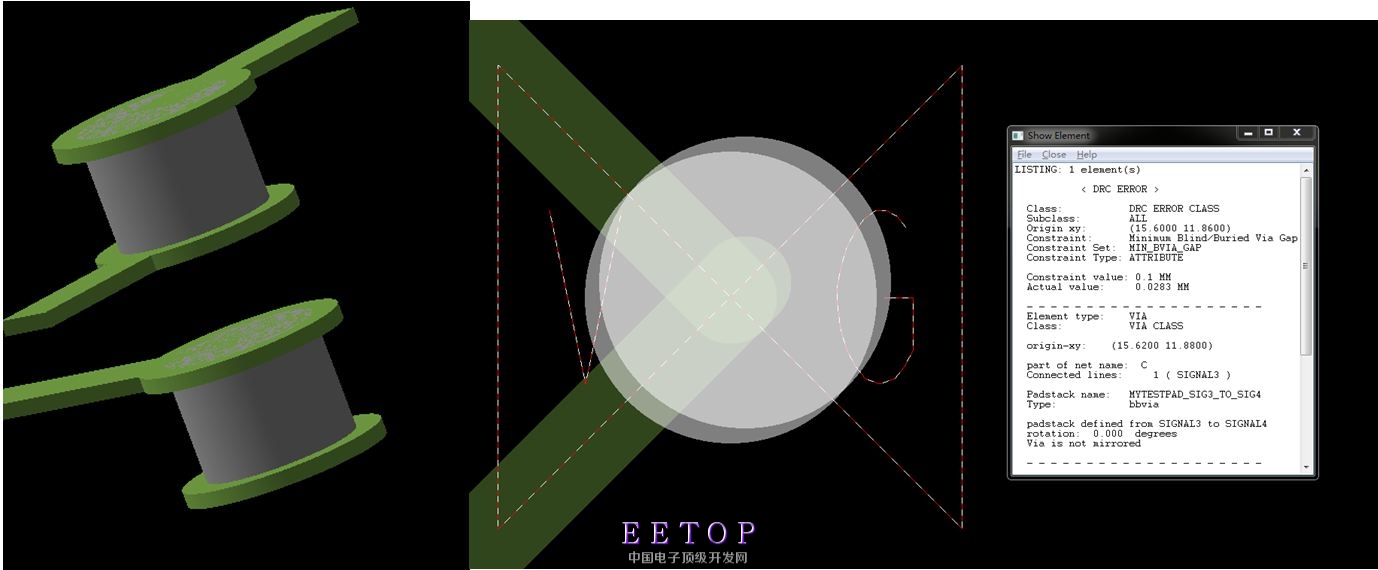

求助,在画一个多层板的时候,上下两层的过孔DRC报错。虽然把对应的constraint 中相应的spacing/net/bbvia gap设成0可以不显示该drc,但是同时也把同层距离过近的via干涉判为正常了。

求助大神正确的解决方法。

< DRC ERROR >

Class:DRC ERROR CLASS

Subclass:ALL

Origin xy:(15.6000 11.8600)

Constraint:Minimum Blind/Buried Via Gap

Constraint Set:MIN_BVIA_GAP

Constraint Type: ATTRIBUTE

Constraint value: 0.1 MM

Actual value:0.0283 MM

求助大神正确的解决方法。

< DRC ERROR >

Class:DRC ERROR CLASS

Subclass:ALL

Origin xy:(15.6000 11.8600)

Constraint:Minimum Blind/Buried Via Gap

Constraint Set:MIN_BVIA_GAP

Constraint Type: ATTRIBUTE

Constraint value: 0.1 MM

Actual value:0.0283 MM

PCB ?