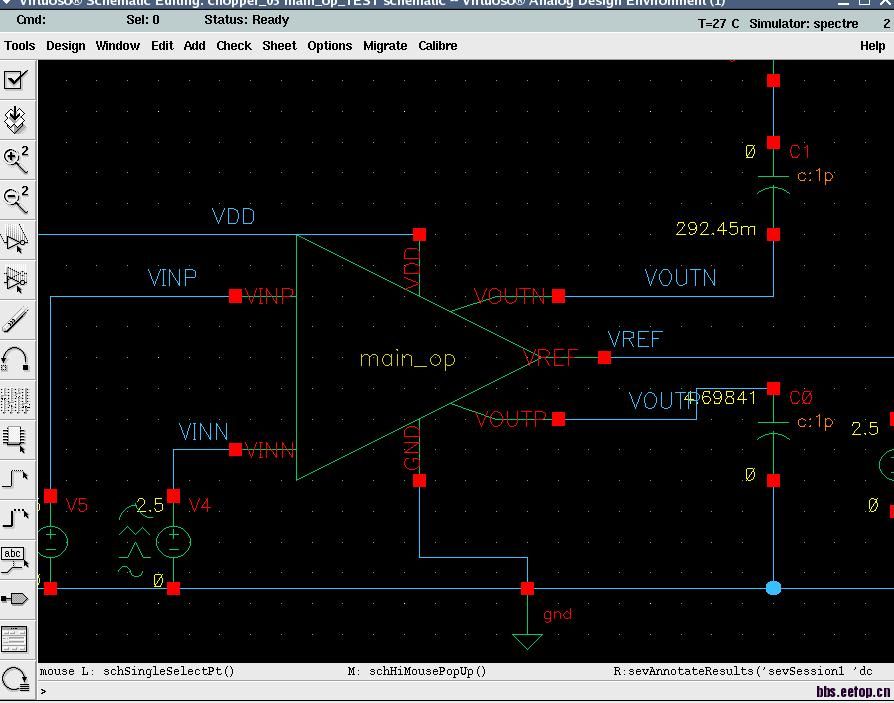

求助,关于后仿真与前仿相差比较大的问题(calibre)

输入管的CASCODE管出现两边电压不一样的现象。而且两端的电压增益也不是完全一样。

想问一下大家:后仿这么差,是什么原因呢 。LVS通过了,电源和VDD的走线宽度也应该够。现在我怀疑是不是信号线平行走的会有互相的影响,剩下的实在不知道为什么增益会下降这么多~

另外全差分的版图设计需要注意什么呢

谢谢各位大神了~

请回复或是PM 啦

全差分运放的版图要注意对称和匹配,版图最好能够呈以某个中轴线对称。

至于小编说的后仿的问题,我如果没猜错的话小编应该是开环下做的仿真,因为后抽取后的运放有很多寄生电阻,这样很难保证运放完全对称

因此就会出现失调电压,如果开环仿真的话,这个失调电压就会让运放输出一个为vdd一个为gnd,这样做AC仿真肯定不正常。

所以如果后仿做AC分析时要接成反馈环路,然后用通直隔交的电路将交流信号的反馈阻断。

小编也可以看看后仿真的瞬态仿真结果,运放应该能正常工作。

所以这个问题应该不是版图的问题而是仿真方法的问题,版图带来的运放失调只能让其尽量小很难避免的。

用mirror吧 把能对称的管子 分half然后对称调用另一半 这样就能确保管子和走线都是对称的

非常感谢,我觉得你说的很对一会我要试一下~

非常感谢space同学的帮助

以后要多多交流

你好,刚才我又试了一下你说的。但是仿真出来,还是一个是地电位一个在高电位。

我现在在想是不是就是版图画的不好的原因呢

另外,后仿测出的失调是6mv不知道是不是很大~谢谢啦

你这还是开环仿真的,输出一个为vdd一个为gnd就是那个失调电压引起的,你做一下后仿的瞬态仿真,运放应该能正常工作。

版图引起6mv的失调应该还不算大

也跟着学习了!

跟着学习一下,我也出现过这个问题,以为是版图设计问题了

呵呵,情况很多,后防器件格式与前防不同也是可能性之一(这个遇到过,是补偿电容,结果是相位裕度严重不足),所以,你得一样一样地排除

讲的很好,谢谢!

讲的很好,谢谢!

嗯,不错

我也遇到了前仿跟后仿失调电压相差几个mv的情况,现在也不知道如何从版图上减小失调电压

不懂电路。帮顶

我后仿的失调是2m,但是增益下降了50dB 不知道该咋整呢

不太懂,有会的没

我也遇到了类似情况,是因为输出那根线画的太细了

1)设计不到位 没有考虑到寄生

2)版图的处理需要提高