求教一个mos管的画法

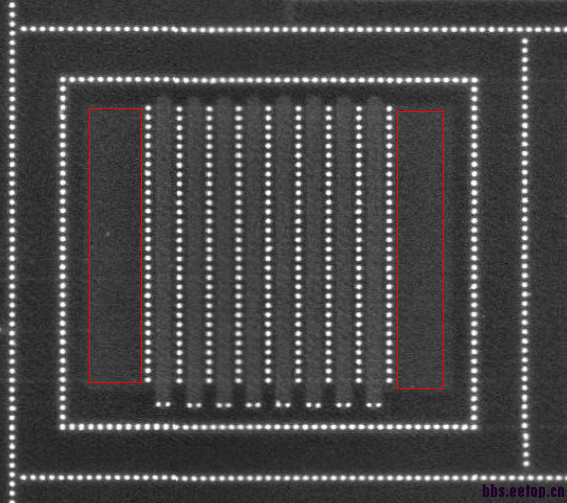

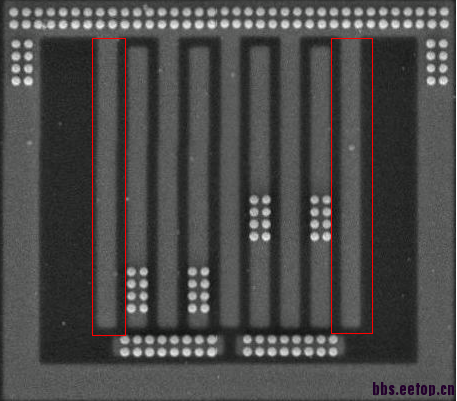

这样的layout画法有什么好处,感觉如果是dummy的话,做上dummy gate不是更好么,感觉只是把diff拉大,contact方式也没改变啊,求大神指教。

不懂,帮顶一下。

不是很明白。

主要是为了减少LOD(Length of Diffusion) effect.

0.25um以下的工艺,都需要考虑LOD effect.

應該是 SOURCE + BODY 才會那麼大

PPLUS 和 NPLUS 在 同一 diff 上

我之前没有这个概念,感谢各位楼上的提示,我据此搜索了一下,搬了网上高手的一篇文章过来。

---------------------------------------------------------------------

LOD Effect——Length Of Diffusion Effect

对于相同大小栅极,因其所在扩散区的相对位置及尺寸大小不同而有不同电学效应,这是由于浅槽沟道隔离(Shallow Trench Isolation,STI)有不同的应力效应,所以又称STI应力效应。 0.25以下工艺大多数采用STI隔离技术,STI会产生许多隔离岛,也产生了不定型或不均匀双轴压应力。处在有源区的应力状态是不均匀的,它与整个有源区的面积有关。 STI主要影响器件的饱和电流(Idsat)和阈值电压(Vth)。 STI延展效应可以通过以下两个参数来描述:SA,SB。这两个参数分别表示栅到有源区两边缘的距离。 MOSFET特性参数如Vth、Idsat, 会因为以下函数变化:

Stress=1/(SA+L/2)+1/(SB+L/2)

其中L指栅长,由此可见,只有当SA、SB均变大时,应力才会变小。以下是STI应力图示,应力大小是有源区大小、MOS管在有源区的位置和MOS管尺寸综合决定的:

上图表明,增加器件到有源区边缘的距离可以减小STI盈利效应,这样就需要为需要保护的器件添加dummy,而且这些dummy必须与被保护器件共享有源区,否则无效。

另外,由于双轴应力增加了空穴的迁移率,减小了电子的迁移率,故随着栅源电压的减小,PMOS的源漏电流增加,而NMOS的漏源电流减小,且SA 、SB越小,效应越明显。而对于非常小的栅源电压,NMOS的漏源电流会突然增加,特别是SA、SB小的时候,这是阈值变化的结果,该变化由应力增强/抑制有源区产生。

感谢大家的提醒,原来没有这个概念

谢谢各位的指点,学习了

学姿势

谢谢各位的指点!