ESD出现大量DRC错误

时间:10-02

整理:3721RD

点击:

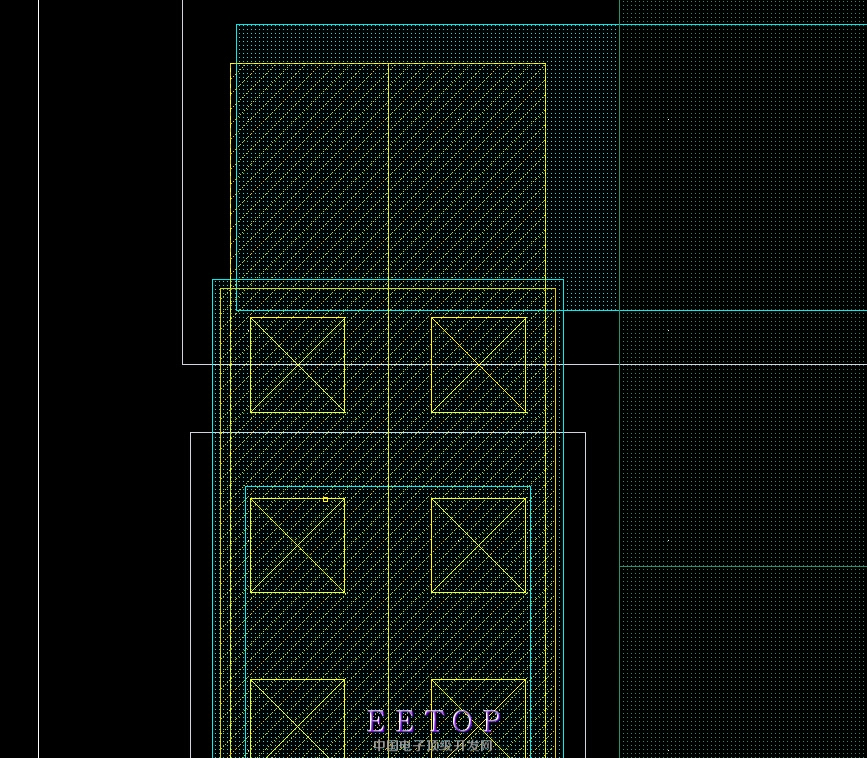

小弟我在流片中,调用之前layout的pad和esd,在跑DRC的时候发现ESD里有各种错误,比如下图中的poly间距,N+imp间距和Metal间距。还有其他各种各样的问题,看了下layout觉得这些间距是不应该报错的,我想请问各位我是否应该修改这些DRC错误?

是不是rule更新了呢?

解决了吗?

之前流片没问题的话,就别改了吧---再搞出点事来---

应该是rule 更新了吧,建议还是联系厂家,沟通一下这个是否有影响?

明显是你哪里搞错了,孔的overlap都动了,有metal 间距违例问题了!

明显是有问题的 metal都没卡齐,POLY也没连上吧。好好检查一下吧

ESD是foundry提供的还是你们自己设计的?

你的layout 肯定被动到了, 6#,7# 都已经指出一部分问题.

谢谢楼上诸位的回答,我也觉得是动过了,有些明显不正确,我回头再找人去要一份

问题解决。出现这种问题的原因是:该ESD是从另一个tapeout的gds中抽出来的。此tapeout是tsmc的mm工艺,而我们用的是BCD工艺,造成了via的错位。可以通过先attach mm的工艺库,将ESD恢复,再打散,再attach回BCD工艺即可。感谢楼上各位的解答

如楼大神所说,layout 没 贴对。