总有人喜欢用多子少子解释guard ring

发现有不少layout engineer在用多子少子解释guard ring的作用,不知道是哪位老师教的,既玄乎又不直观还不准确。

有两种ring:

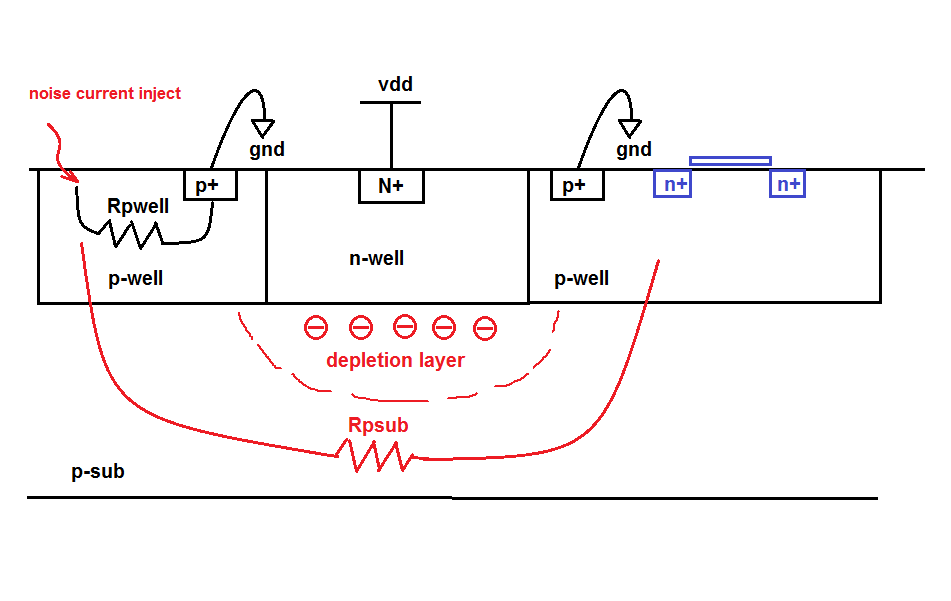

ptap, psub pick up,接到地,提供低阻通路,把noise电流泄放掉。

nwell ring,利用反向pn在psub上产生的depletion layer提高噪声耦合路径的电阻,使得噪声衰减。

还有几个问题是用多子少子解释比较牵强的

1. nwell ring真的吸收了电子吗?pn 结反偏,是高阻状态,只有极少的反向漏电流,此外就是反向pn结耗尽层电容,因此nwell ring吸收不了噪声电流。

2. 对于隔离,大家通常会增加space,使两个模块远离,多子少子情况又是什么样呢?

3. 还有一种做隔离的方法, native psub,该区域没有pwell

4. deep nwell ring隔离效果会比nwell ring更好,多子少子和nwell ring 有什么差别?

总结一下,deep nwell ring/nwell ring 效果最好,其次是native pusb 或增加space,ptap

小编可以详细的解释一下吗?

玄乎?呵呵。

“ptap, psub pick up,接到地,提供低阻通路,把noise电流泄放掉”——低阻通路是给谁提供的?难道是光子?noise电流难道是家里水龙头里的水分子形成的?

“nwell ring,利用反向pn在psub上产生的depletion layer提高噪声耦合路径的电阻,使得噪声衰减”——有这方面的作用,但是更主要的是NWELL阻挡了载流子的路径,使大部分载流子不能跑到其他地方去,对于P衬底工艺主要是阻挡了多子空穴和能量小的少子电子,能量大的电子进入nwell被泄放了。

看问题的角度不同而已。大部分layout工程师都不太懂电路,如果用电路的原理去解释可能很多人不明白。layout工程师可能有一些工艺基础,用载流子去解释会容易理解一些。

要说直观,用载流子解释也肯定是最直观的,原因很简单,电路工作的本质是电子的运动。

顶下,等待高手解答!

那敢问小编你说的noise电流不就是多子少子的流动吗?

能否解释一下ptap?

我觉得应该和nwell的原理差不多吧,并不是提供所谓的低阻通路吧,求解释啊!

站在电荷的角度看,原理是一样的,但是非要分空穴和电子的话就有区别。多子保护主要是为了吸收乱跑的多子,既然要吸收,那就要给多子提供一个低阻通道,让多子更容易被吸走,所以这样说也是没错的;少子保护是为了吸收少子,道理同吸收多子。但是同时呢,多子保护也能起到阻挡少子的作用,少子保护也能起到阻挡多子的作用。为什么?因为电子总是往最高电位的地方跑,而空穴总是往最低电位的地方跑,当然本质上只有电子在动。

以P衬底为例,多子保护是P,比如Ptap,少子保护是N,比如Nwell,Ptap接地,Nwell接电源。接地的Ptap可以吸收多子空穴(指那些不希望出现的衬底电流中的空穴),可以排斥少子电子(也是不希望出现的);接电源的Nwell可以吸收少子电子(不希望出现的),排斥多子空穴(不希望出现的)。保护的原理可以分为两部分来看,一部分的空穴或电子被吸走了,一部分的空穴或电子被挡住了,被吸走是最理想的,不会影响任何电路,吸不走的就被挡住,虽然没有被吸走好,但是至少可以保证不影响其他地方的衬底。Nwell一般比ptap深得多,所以可以起到的阻挡作用比ptap强得多。只要不是大注入或很高的温度,我认为Nwell的阻挡作用比吸收作用更重要,因为毕竟衬底里面起作用的主要还是空穴。

小编,只用“多子少子”解释guard ring有点片面,但应该和其他方法结合起来,也不能撇开“多子少子”,毕竟噪声的本质还是要追溯到电子的。

如何说明 “ptap, psub pick up,接到地,提供低阻通路,把noise电流泄放掉”不准确啊?

“更主要的是NWELL阻挡了载流子的路径,使大部分载流子不能跑到其他地方去,对于P衬底工艺主要是阻挡了多子空穴和能量小的少子电子,能量大的电子进入nwell被泄放了”,你的意思是pn结被反向击穿了,有电流通过了?

你这个理解对nwell有本质的问题。反偏的pn结有很强的少子收集能力,而不仅仅是一个高阻。这个在半导体物理里和晶体管原理里都有体现。反偏pn结之所以电流很小,不是电压不够,而是载流子不够,所以如果附近有载流子,会被电场马上拉过去,起到很强的伪收集级作用。

少子多了反偏pn结就有电流了?

一般所说的“PN被击穿”是一种宏观现象了,就是PN结某点电场强度太大导致齐纳或雪崩击穿。但是在微观上,半导体中时时处处有电子和空穴被激发出来、被复合,而且电子不停地做运动,有热运动,有因为电场的漂移运动,也有浓度梯度造成的扩散运动。其中总有一些电子或空穴的能量达到或超过PN结的势垒从而可以穿过耗尽区,或者到达PN结边缘时能量不足以穿过,但是会被PN结反偏的强电场拉过耗尽区。然而这些电子或空穴的数量是很有限的,不足以形成宏观上观察到的击穿的电流。

这还牵涉到对“噪声”的理解。我觉得噪声在本质上一是正常电流通路以外的载流子闯进来了,二是正常电流通路中的载流子跑出去了,三是载流子没有按照预设的方向流动。guardring的作用就是从这三个方面来考虑,广义的guardring并不只是指模块和模块之间的guardring,器件和器件之间的其实也是,比如每个PMOS旁边的ntap和NMOS旁边的ptap都是起到了guardring的作用,防止latch up在本质上也就是防止噪声。

如果你坚持用多子少子解释guard ring,那实际当中画多宽的guard ring就够了?

画好了guard ring能够达到多少dB的isolation?比如说我要实现40dB的隔离,那么应该怎么画guard ring?

是不是画layout全凭经验或者感觉,或者完全取决于今天的心情或天气......

我说了,只是看问题的角度不同,多子少子不过是在物理层面上理解,如果理论正确,不管从哪个角度解释都没错。实际中当然还是要依靠电路理论去计算了,否则我还要把I=Q/t重新定义一下......。

那么你认为bipolar的bc结反偏,c级电流是怎么出现的?

没有be结正偏,能冲破反向pn结势垒?

那你画条guard ring,算个隔离度试试,画多少算是够了?

用多子少子是没法算清楚guard ring的隔离作用的,赶紧抛弃这种陈旧的观念吧

用电阻模型很容易就可以估算出guard ring 的隔离效果啦

只需要在layout 上量一下距离就差不多啦

gaojun927:不要再纠缠了,这个帖子到此为止。

也许大家各自的出发点就不同。先说什么是干扰,在pll等电路里,数字电路引起ground bounce,然后通过衬底影响到vco,这是一种干扰。功率器件里一开一关,使得周边的电路几乎无法正常工作,这也是一种干扰。你喜欢用隔离度来举例子,也许在有的情况下,另一个人喜欢用晶体管的beta来反映抑制能力(这不是虚构的),其实无非是根据个人碰到的实际情况来建造一个合适的模型而已。

请问电子和空穴在电场中的运动方向?你会理解别人为什么说多子少子,另外,pn结的势垒图也可以好好看看,有用的哈

又不是不知到多子少子,问题是这种理论毫无实践指导意义

有些整天就知道用多子少子忽悠人

我让具体算一个guard ring的隔离度,结果都哑巴了

就知道用多子少子理论在做guard ring的layout engineer有多浮夸多虚了

那你就说说隔离度怎么算吧,好让我们开开眼,以前不知道这个概念啊!

isolation(dB)=20*log(noise couple path imepdance/local pick up gound impedance)

举个简单例子

噪声源从衬底耦合到受保护模块,这个路径电阻100欧姆,

受保护模块的衬底ptap和gnd电阻1欧姆

那么噪声源的地有100mV的ground bounce,到我们受保护模块的地就会有大约1mV的干扰

至于如可估算噪声耦合路径的电阻,这就需要个人的基础扎实,知识全面,对半导体工艺制程熟悉了

能否解释的再清楚些,最起码解释解释你的公式啊!

公式?电阻分压不会算啊,100ohm 串联1ohm

... 我无语了

我是让你解释解释公式中衬底ptap电阻的估算好不好

ptap电阻 pwell电阻+ p+电阻 + contact 电阻+ metal routing电阻

说的没错,但是是分布式还是集总参数,你这个还是应该说清楚如果按你这个表达式,我们理解为集总参数,那么对实际又有何作用。

你问别个,别个没有用电子和空穴给你解释清楚,第一,可能确实别人理解不够深入,这个确实需要理解能力和时间的积累

第二,别人解释清楚了,但是你总是纠结在多子少子,所以处处为难别人,这个就是你的不对了哈

总之,问题是用来讨论的,不是用来做人身攻击的。

如果自己没有理解清楚,可以看看《the art of analog layout》guardring那一章节,另外基本的电场理论还是需要的,我觉得这个是认识这个问题的根本