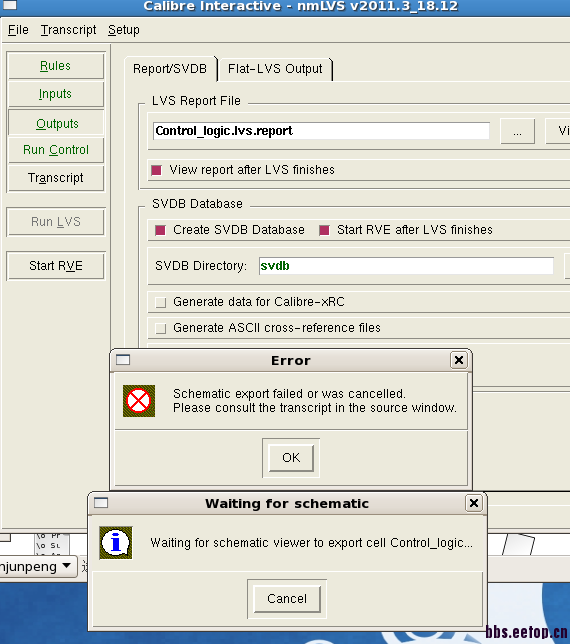

Calibre LVS时遇到问题

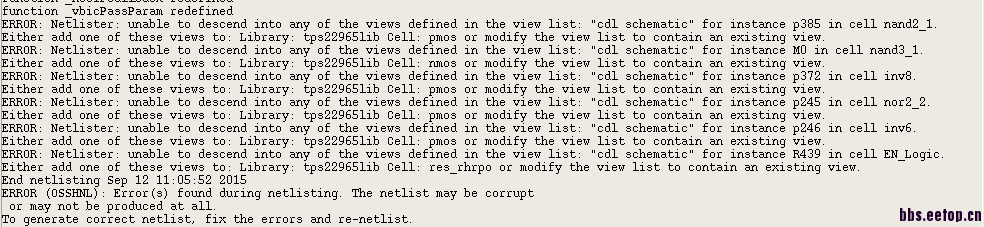

这个是CIW显示的错误信息

我用手动提取cdl却能提取出来,也找了些解决方法,例如删除Layout和Schematic文件夹里面的.cdslck文件,但是还是不行,求大神帮忙

第一次用在输入那里用自己提取的 网表,去掉exportfromlayout viewer,下一次就可以用了

1。不知道是不是你设置错了,就在你发的图片LVS窗口中,Inputs --Netlist--Export from schematic viewer 要选上。2. 在你跑的top层shematic --Check-Hierarchy check.所有的doucheck一遍,是否有错。3.shematic中是否有调用空的symbol,例如PR routing 的模块,需要把这部分的CDL include到总的里面去。希望对你有所帮助!

还是不行,我用自己expert>CDL提取的网表跑了后,想用软件自己提取的网表还是显示错误

1.有勾上。2.我每个模块都check and save了还是不行。至于第3点我有点不懂是什么意思

第三点是说,你的shematic是否调用了STDCEL 库中的symbol, 那个是没有shematic的,只有symbol,手动抽取cdl是,系统会自动把STDcell 库的cdl, include 进去。而在LVS窗口直接RUN, 这一部分的cdl 并没有加进去,所有跑不了,说你的cdl 报错。你可以打开你手动抽取的cdl, 查看一下,是否 含有: INCLUDE/home/lib/... 这些字样。跟LVS直接跑出来的做个对比,看看是不是这个错误。

你的电路图有更改,需要check and save才能提网表

我遇到了相同的问题,得看 icfb的报错信息,我的是

cadence/IC514156145/tools/dfII/bin/64bit/si.exe: error while loading shared libraries: libg2c.so.0: wrong ELF class: ELFCLASS32

把 配置文件.cshrc 中的CDS_64BIT_AUTO 去掉,就行了

学习了