大家差分对的布线是怎样的呢?

时间:10-02

整理:3721RD

点击:

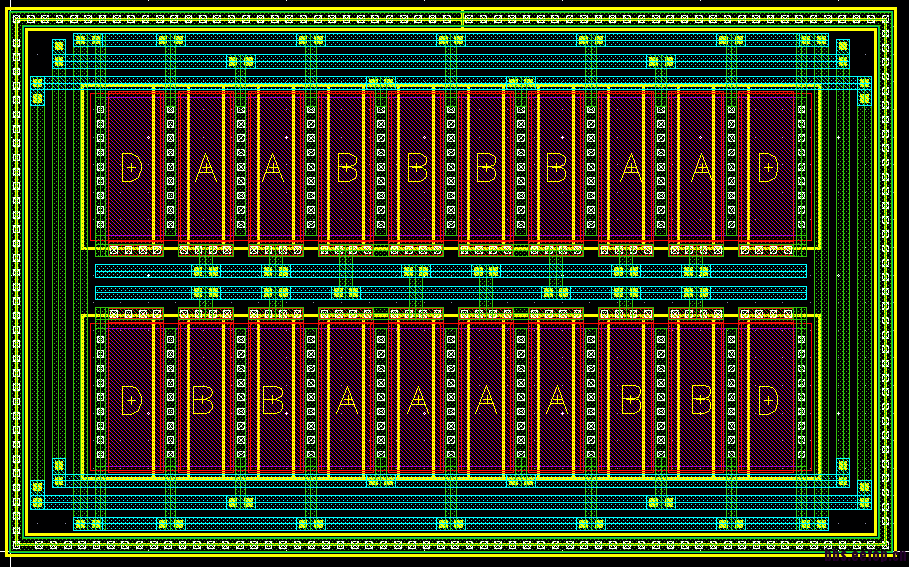

下图是我画的差分对,这样画是为了方便横向的差分输入信号好走出去,但差分的输出不好对称,不知道怎么处理差分的输出信号比较好?此处只想用到两层金属。(我在外面都是横向金属1(绿色),纵向金属2(蓝色)的走线)

你这不是已经挺好了吗

如果跟负载做成上下结构的话,输出不好匹配

这样子大致没什么大问题,具体负载的连接还是要看你的位置摆放,还有走线的影响,你画的应该是制程大一些的,后仿应该没什么问题

一定要把A 和B共用的一端和各自的另外一端 三条线做成一个封闭的环形吗?

搞成一排AABBAABB,走线会容易很多,出线这么细,过大电流就有问题,gate的线细一点没有关系

现在我一般都做成AAAABBBB,不要太在乎各种花里胡哨的排列,那些有时只是心里作用

在现在小尺寸的工艺下,就这么小的两个mos也就几个um十几个um,梯度影响并不明显

所以能简化就简化,反而要好好考虑各种新的效应,比如LOD,WPE,OSE,PSE的效应

要看具体情况了,这真就不好说

以前在学校老师是这样教的,两个环做成这样内插的形式,两组输出的路径长度会一样。也不知道这样到底好不好

书上说ABBA是最经典最好的模型,但是发现前辈们也喜欢用AABB的模型,二维的话就再加一排BBAA。不知道哪种好一点?

对,制程是比较大,0.18um的。负载放两边的话还好,但是放下方的时候输出不好接,又不想把环破开。

谢谢!大制程的工艺一般不考虑这些效应?