关于过孔层叠

时间:10-02

整理:3721RD

点击:

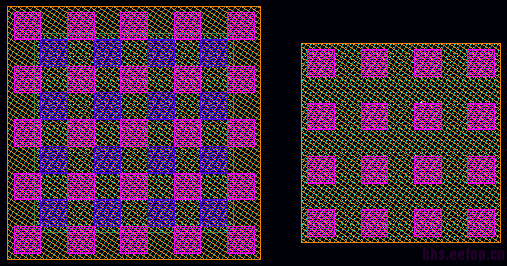

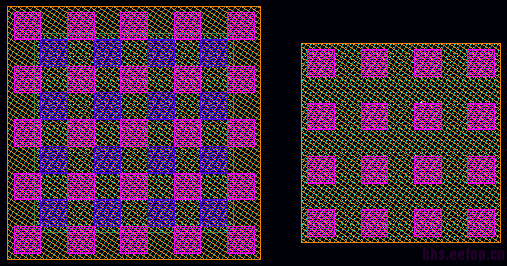

关于layout里面的过孔重叠,不知道是交叉层叠好呢还是覆盖层叠好呢?如下图都是从metal1→metal3,左边是交叉via1、via2,而右边是via1完全覆盖via2,哪一种层叠方式更好呢?

左边那种好一点。

从某些工艺的design rule里说VIA2 覆盖VIA1是允许的可以推断,有另外一些工艺是不允许VIA2覆盖VIA1的。(如果都是允许的,何必要说这句话呢。)

所以,个人由此觉得图中左边那种应该要好一点。

如有不正,欢迎指出。

这个应该和工艺也有点关系吧,看一下design rule 后面有关的via单孔的过电流能力以及vias叠加后的过电流能力就可以分辨了。

左好。工艺上的人说在都允许的情况下左边的对散热有些好处,不知道啥道理。

某些老工艺无法生产出层叠的孔,所以design rule中会标明允许&不允许层叠。

个人觉得如果没有特别说明不能交叠那就怎么方便怎么来。没啥好坏的。都一样。

我认为右边的效果好,电流速度快

一般不是流大电流或者ESD处,很少考虑吧!stack的话画起来效率更高,面积也省

都可以,只要工艺迟迟

同意 左邊比較好

个人觉得如果很小的3X3以下,一般是重叠的,比较方便,如果是大面积的话,还是左边的好一些

现在工艺进步了 都是后者了

感谢各位的积极指导,从散热和工艺的角度估计左边的好些,从面积和效率角度右面的好些。使用的时候折衷考虑吧