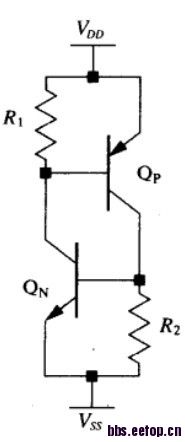

CMOS工艺中背栅有助于防止闩锁效应?

这个图怎么理解呢?求高人指点。

而在cmos中加背栅怎么就可以防止闩锁效应呢?

去看《模拟电路版图的艺术》第4章少子注入那一节你就能明白第一个问题了。

加背栅是防止源/漏与衬底的PN结正偏,也就是防止寄生晶体管开启,管子不开启,就没有闩锁效应了撒~

我知道那个书的,也看了,图就是从那里借来的,但是还是我太没明白。

有助于防止闩锁效应,增加背栅的连接有助于减小图中R1和R2的阻值,但是不可能无限减小,R1/R2减小了有助于提高latchup的防护性能

哪里没明白,还是背栅问题?

“有助于防止闩锁效应,增加背栅的连接有助于减小图中R1和R2的阻值,但是不可能无限减小,R1/R2减小了有助于提高latchup的防护性能”

这个好理解一些。

只是明白的有些晚。不过今天听到一个解释说,如果加了背栅,那么会使得寄生管发射极短路,那样就不能形成闩锁了。

“有助于防止闩锁效应,增加背栅的连接有助于减小图中R1和R2的阻值,但是不可能无限减小,R1/R2减小了有助于提高latchup的防护性能”

这个好理解一些。

只是明白的有些晚。不过今天听到一个解释说,如果加了背栅,那么会使得寄生管发射极短路,那样就不能形成闩锁了。

受教了,谢谢分享~

各位指的加背栅如何实现?在衬底加负压或在NWELL上加大于VDD的电压?

弱弱的问一句 什么是 背栅?

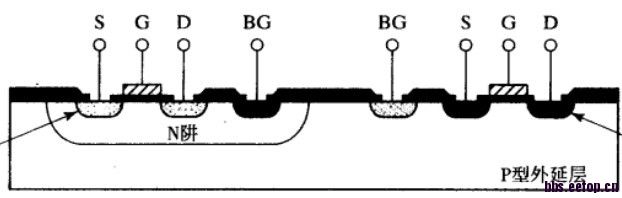

在mos晶体管中,有几个端口,分别命名为s(源极),d(漏极),g(栅极),bg(背栅)。比如PMOS的背栅是NWELL

所谓加背栅就是增加背栅浓度(NMOS)、减小衬底浓度(PMOS)以提高阈值电压。所谓背栅,对PMOS来说就是N阱,对NMOS来说,就是P衬底。

那個 在台灣就 mos 的 Bulk ... 一般就是 多打 pick_up

N_well 讓電位拉高降低 被 noise trig ..

降低 r1 r2 ..應該沒法吧

因為 process 沒法調阿 ..

减少R1,R2的是背栅的掺杂浓度吧,所谓的加背栅是指加背栅电位?还是背栅浓度啊?