请教SDRAM的CAS

时间:12-12

整理:3721RD

点击:

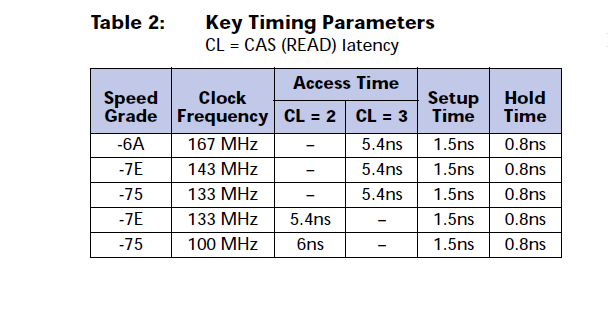

附件是一个SDRAM的CAS参数表,我的理解是: SDRAM 在选定列地址,确定存储单元后,由于存储体中晶体管的反应时间, 数据需要经过一段时间才能输出,但表中的数据不能理解

对speed grade 为-75的133MHz , 如果CL=3的话,那么 CL= 3*7.5=22.5ns 为什么表中标的是5.4ns呢?

还有 speed grade 为-75的100MHz , 和 speed grade 为-75的133MHz ,是指参数完全相同的器件可以跑在不同的速度上 还是指的是两个参数不完全相同的器件? 初次接触SDRAM,望指教 谢谢了!

对speed grade 为-75的133MHz , 如果CL=3的话,那么 CL= 3*7.5=22.5ns 为什么表中标的是5.4ns呢?

还有 speed grade 为-75的100MHz , 和 speed grade 为-75的133MHz ,是指参数完全相同的器件可以跑在不同的速度上 还是指的是两个参数不完全相同的器件? 初次接触SDRAM,望指教 谢谢了!

那么 CL= 3*7.5=22.5ns

这句不对。Tac应该是指 读操作中 给sdram的clk posedge之后多长时间数据线上稳定。

比如cl=3 Tac=6ns。代表你给sdram的第三个上升沿之后6ns 数据线上有数据

貌似你混淆了CL(CAS Latence)、tAC(Access Time)、以及数据访问总延迟的概念。附图应该很好地说明了CL和tAC的含义。

CL反映的是CAS选通后过多久读数据逻辑开始发出来(被时钟边沿所同步),而tAC相当于将被同步的数据再稍微提前一点,以保证(接收端)在时钟的边沿(锁入时)对应上数据的“稳态”而不是过渡态(加上传输延迟差就相当于提供了一个建立时间)。图示中实现这个目的用的提前一个CLK然后延迟一段时间(tAC),因为需要的是比同步提前前,不可能等这个时钟访问的时钟到来后再去提前。所以实际的提前量是要用一个时钟去减tAC的。

多谢多谢!