DAC求助

这个难道不是先大概知道面积功耗了,然后才有sfdr吗?电路好了的时候,layout应该也差不多好了吧。

这个肯定是先画了unit cell,然后把寄生提出来做仿真,然后有两个iteration之后再画整体的layout

看你的设计指标是多少,前仿真满足要求了就开始做layout呗。。。

提醒仿真时留适当的裕量给芯片内寄生及芯片外封装和应用、测试环境中的非理想因素。

如果速度不快,例如fs<200MS/s,那么那些影响比较小,如果>500MS/s影响相对明显得多。

宽带的DAC的版图寄生对sfdr的影响很大,如果前仿时对这些寄生效应预估得准,那layout也就差不多了。

哦,我现在是先设计电路啊,没有电路我没法画版图啊。。。面积功耗决定SFDR?

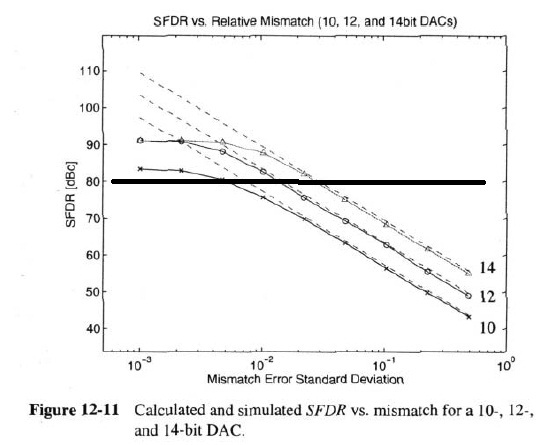

我的采样频率是200M HZ,我觉得做到80多应该可以了,我还有一个问题,就是mismatch的事情,这个东西仿真防不出来我应该如何尽量减小呢?

全频段80多并不容易做,这两年t-cas上200MS/s nyquist DAC的SFDR最高也就80出头。

mismatch为什么仿不出来?

目前减小的方法大致也就这么几个:校正,版图技术,考虑管子尺寸和静态工作点的电路设计方法。另外用dem也可以考虑。

他说的也有些道理,主要是数字部分的二进制到温度计码译码器的面积和功耗跟温度计码位数关联比较大。除此外,生做的话没觉得堆砌面积和功耗可以提高sfdr。

原来是做DAC的高手啊

请教个问题,SFDR的约束条件有些啥

比如说在14/12bit ,200M的clock下,器件失配,还是输出阻抗?

这两年t-cas上200MS/s nyquist DAC的SFDR最高也就80出头,你说的是仿真结果还是流片测试结果?

数字部分是应该写代码综合出来呢,还是用模拟的方法画出来?

话说现在14b 200M这个DAC 电流舵是生做还是用DEM?

按照这个参考资料,14b的SFDR要做到80db的,电流舵的size不会小啊。

你说的size是指管子的尺寸还是指总的版图面积?

我不敢当。。。大家有目共睹,您才是版上的大牛。。。。

我个人认为sfdr的约束条件比较多,器件失配,输出阻抗,控制信号和各电流输出支路的同步,控制信号引入的glitch,时钟质量等,都是影响因素。每个因素的影响程度要控制在什么范围内跟信号频率、期望的sfdr都有关系,而且比较复杂,有一些因素与sfdr之间好像还没有清晰的数学关系,但能大致地定性分析。broadcom@isscc/jssc2009, adi@isscc2012, 台湾新竹国立交通大学@isscc2011/jssc2011/isscc2013上的几篇文章我觉得很有启发,他们对一些因素的研究比较深入(parasitic capacitance, CS mismatch, code-dependent transition nonlinearity)。

我做DAC的时间不长,平时主要靠eda工具仿真。理论分析做得不多。

一些观点可能不正确,thucat见笑了

上面发表的一般都是流片结果,当然,我说的是nyquist sfdr。

如果低频的话,adi之前发了16b 400MS/s的,低频下做到了SFDR>90dB

我看到的都有,我在学校画过6位译码器@1GS/s,零散时间,大概花了2~3个星期。

我当时选择自己画的原因是,听说要综合1GHz的时钟下的这个电路很困难,所以就自己动手画了。

他那个图应该是当年谭年熊发表在tcas-II上的一篇文章上的数据。

我建议参考一下Sansen小组发表在iscas2000上的文章,an accurate statistical yield model for cmos current-steering D/A converters。

根据一定的INL产率要求可以推导出LSB电流源的电流匹配要求。

如果生做,可再去查一下fab工艺手册,看晶体管要什么尺寸才够保证匹配。

这个尺寸要在具体管子的工作点下才有意义。

另外,ir drop, fab的gradient matching error都会影响inl

似乎要做到80dB不一定要14bit

而且通过大尺寸搞定了14bit的精度,很可能sfdr更差,

因为寄生增加可能使输出阻抗达不到要求。

显然不行。芯片pad等,pcb上的走线,还没算你测试设备的负载。

我不确定我们的工具能是否做蒙特卡洛分析,一会回去试试,手算的话怎么计算呢?

我这仿真还没好呢?版图也没画呢,哪有时间想这个?

所以我问你有没有测试方案,因为你的DAC是需要驱动后面电路的,所以要根据后面的电路输入负载来定。

dac的测试应该比较头疼。

我估计仿真的时候至少5pF。

建议你多请教qingxinboy等。翻他的帖子,他刚刚做完DAC。

线性的输出负载电容主要影响settling time,不容易影响sfdr。

你可以尝试推导一下,或者仿一下都能看出来。

可参考jssc2009年12月的那文章,和isscc2009同作者的12bit 2.9GS/s DAC

测试可以参考一下agilent提供的adc/dac测试方案

就200MS/s速率,生成数字码型可以考虑用agilent逻分16800/16900系列的;

也可以考虑用fpga。似乎之前在版上讨论过一次。

你的dac是current-steering的吧?它可以直接驱动阻性负载,包括同轴50ohm负载。

只是输出还要用个差单转换,这些东西文章上,或者adi/ti的手册上都很常见。