问一下做前端的,一般一个电路的Timing slack有多少啊?

我不是Designer,我是搞DFM的,所以我关心这些……

你这个问题在水源上问过 ,DFM 跟这个没有关系吧

其实Slack肯定要Meet, WC也要过的

一般都是过约束,

打个8折, 后端要布线就吃掉了

我其实感兴趣的是,最后的path delay,ff : nom : ss 是多少

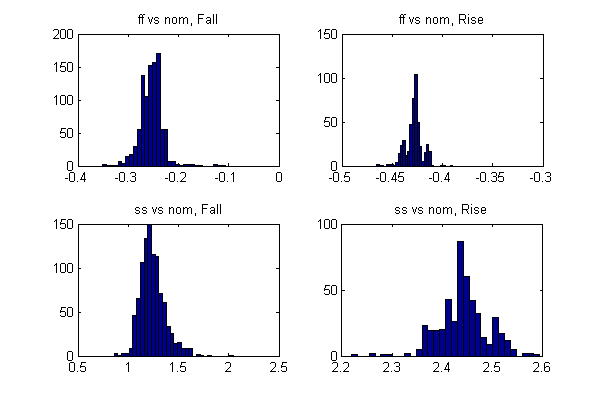

我手动hspice了一个纯组合电路,(ff-nom)/nom以及(ss-nom)/nom的histogram如下图:

我把output falling edge和rising edge分开画了。于是发现path delay 基本上是:

Fall: 0.75 : 1 : 2.25

Rise: 0.6 : 1 : 3.45

其中mean(nom_fall) : mean(nom_rise) = 0.5 : 1

撇开fall和rise之间的差异,大体上应该就是说明了ss比nom和ff慢多了对吧?

这样啊,认知颠覆了。我认为FF/SS应该cover gate length variation,找个机会问问公司的spice相关的工程师好了。

其实,没有人这么做的

我们做前段,就看WC,最差的情况,有很多的Cell

一个Cell没有代表性

Timeing就选WC然后就可以了

你自己做了这么一个分析,组合电路

一般来说都是前后 加了Register就把Timing隔离了

我的意思是,一条path指得是两个register之间的那段纯组合电路

那就对了,2个REG之间的纯组合电路一半都是WC分析的

90nm 工艺以下还要分析OCV SS是必须Meet的,比如我CPU综合600,实际后端做完,我们的系统只能跑480左右

你的用的Cell 应该有HVT LVT 等等才行吧

我明白了,你的Slack做综合的时候,就是选0 就可以了,

这样constrain 尽可能的过约束,时钟频率最高值H*0。8(当然你需要去后端问一下系数)

得到系统最终的估计时钟

你这个flow有点老了吧,现在DC-T出来的timing和最后layout出来的timing基本一致了,没有8折这种说法了。另外现在用的都是ccs model

还有这种说法,overcontrain 应该是比较好的方法了

你有这方面的介绍,搞来我看看~