问一个关于Reset同步器的问题

时间:12-12

整理:3721RD

点击:

从书上看到的:<Advanced FPGA Design>,(其实还有其它文章也有推荐这样的结构)

SNUG paper “

Synchronous Resets? Asynchronous Resets?

I am so confused!

How will I ever know which to use?

” 也同样提到这种结构~

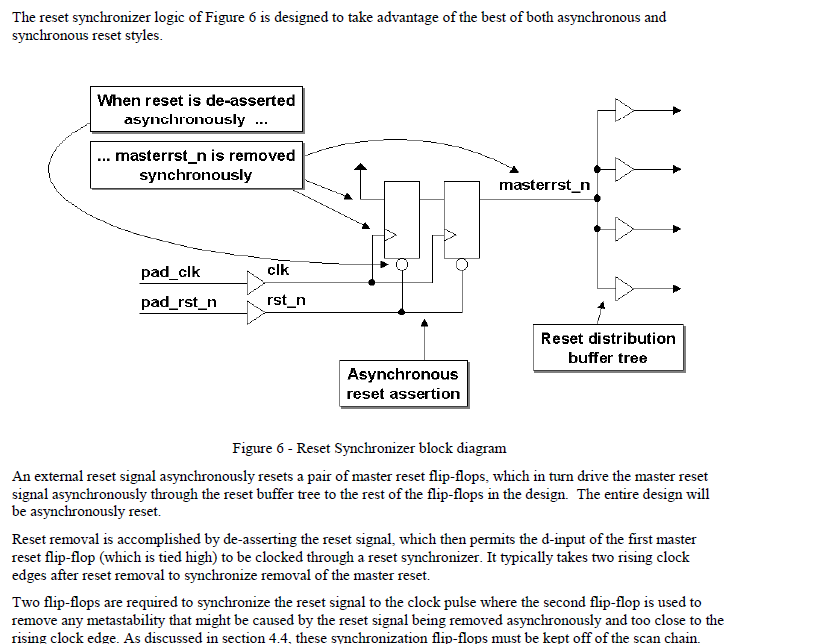

Asynchronous Assertion, Synchronous Deassertion

the registers in the reset circuit are asynchronously reset via the external

signal, and all functional registers are reset at the same time. This occurs

asynchronous with the clock, which does not need to be running at the time of

the reset. When the external reset deasserts, the clock local to that domain

must toggle twice before the functional registers are taken out of reset.

Note that the functional registers are taken out of reset only when the clock

begins to toggle and is done so synchronously.

我想在如下情况下还能正常工作吗?

当这两个用于的同步的寄存器,都出现了Recovery Timing Violation,

造成他们的输出都是亚稳态,这样右侧的那个寄存器输出的X态会去驱动Reset Tree而造成

System Flip-Flops根据自己收到的X态进行判决,造成有的退出了Reset状态,有的还处于

X态。 此时系统还是不稳的,不符合设计期望(所有寄存器同时退出复位态)。

如果所幸,在下一个edge来的时候,右侧的那个同步寄存器将前一级的X态判决为0,这样又

可以吧System Flip-Flops置于Reset状态,再过一个T后,在Reset Tree上又会看到从Vcc同步过来的1,将System Flip-Flops带出Reset态。这样没有问题。

如果不幸的是,在下一个edge来的时候,右侧的那个同步寄存器将前一级的X态判决为1.这样就会保留之前的那个现象:有的先退出Reset状态,有的后退出Reset态.

或者各位是这么理解这个电路的工作流程及原理的呢?

SNUG paper “

Synchronous Resets? Asynchronous Resets?

I am so confused!

How will I ever know which to use?

” 也同样提到这种结构~

Asynchronous Assertion, Synchronous Deassertion

the registers in the reset circuit are asynchronously reset via the external

signal, and all functional registers are reset at the same time. This occurs

asynchronous with the clock, which does not need to be running at the time of

the reset. When the external reset deasserts, the clock local to that domain

must toggle twice before the functional registers are taken out of reset.

Note that the functional registers are taken out of reset only when the clock

begins to toggle and is done so synchronously.

我想在如下情况下还能正常工作吗?

当这两个用于的同步的寄存器,都出现了Recovery Timing Violation,

造成他们的输出都是亚稳态,这样右侧的那个寄存器输出的X态会去驱动Reset Tree而造成

System Flip-Flops根据自己收到的X态进行判决,造成有的退出了Reset状态,有的还处于

X态。 此时系统还是不稳的,不符合设计期望(所有寄存器同时退出复位态)。

如果所幸,在下一个edge来的时候,右侧的那个同步寄存器将前一级的X态判决为0,这样又

可以吧System Flip-Flops置于Reset状态,再过一个T后,在Reset Tree上又会看到从Vcc同步过来的1,将System Flip-Flops带出Reset态。这样没有问题。

如果不幸的是,在下一个edge来的时候,右侧的那个同步寄存器将前一级的X态判决为1.这样就会保留之前的那个现象:有的先退出Reset状态,有的后退出Reset态.

或者各位是这么理解这个电路的工作流程及原理的呢?

异步复位,同步恢复的结构。

就是怕rst释放的时候跟clk打进上升沿让 ff产生不定态。所以用这种结构让rst恢复的时候跟clk同步。同时又保留了异步复位的特性。

在reset释放后的clock edge,第一个寄存器的输入是1,可能会造成其输出是亚稳态

同时,第二个寄存器的输入应该是0,它的输出也应该是0吧,会是亚稳态吗?

第二个clock edge时,第一个寄存器采到1,第二个寄存器采到亚稳态,可能输出1或0

第三个edge就都没事了。。。