ASIC pioneer reinvents 3-D FPGAs

时间:12-12

整理:3721RD

点击:

PORTLAND, Ore.—Serial entrepreneur Zvi Or-Bach is touting a three-dimensional field-programmable gate array (FPGA) technology that he claims could achieve the densities of an application specific integrated circuit (ASIC). Or-Bach's new company, NuPGA, presented details about its 3-D FPGA technology Friday (Jan. 29) at the Applied Materials Technical Symposium on 3-D Interconnect in Santa Clara, Calif.

Or-Bach, a past winner of the EE Times Innovator of the Year Award, previously pioneered ASICs at eASIC and later at Chip Express. Last year, Or-Bach applied for a patent with Rice University on a graphite-based memory process for creating reprogrammable memory elements, which NuPGA is now using as anti-fuses for its 3D FPGAs.

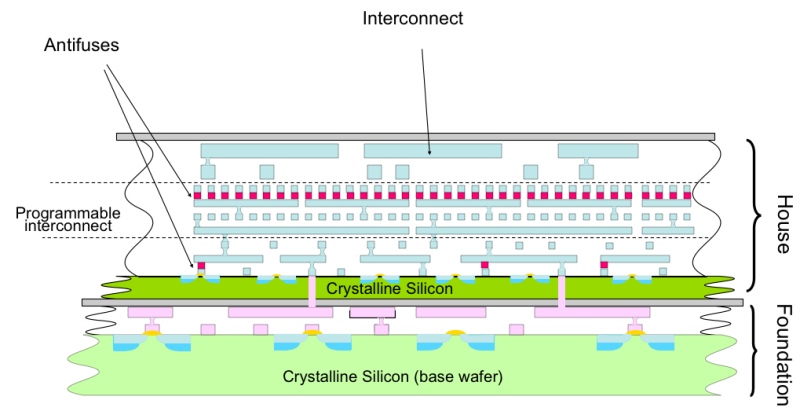

NuPGA's anti-fuses start out as an open circuit but can be reprogrammed to create a low-resistance connection when pulsed with a high voltage. By arranging anti-fuses in a separate layer above logic, they could boost the interconnection density of FPGAs to rival ASICs, according to Or-Bach. The only problem is that the high-voltage programming transistors take up so much room that they negate the density boost. NuPGA claims to have solved that problem by burying the programming transistors in a 3-D "foundation" layer beneath the traditional FPGA circuitry.

By building a foundation wafer housing all the bulking programming transistors atop a conventional wafer holding logic and interconnect, a 3D FPGA achieves the density of an ASIC (click on image to enlarge).

"The number one deficiency of anti-fuse FPGAs is the area consumed by the high voltage transistors you need for programming," said Or-Bach, founder, president and CEO of NuPGA. "But by moving these transistors underneath in 3D, the FPGA becomes as dense as an ASIC."

NuPGA's 3-D construction technique first fabricates a foundation wafer containing the high-voltage programming transistors interconnected by high-temperature tungsten metalization and capped with an oxide layer. Then a second blank silicon wafer is capped with oxide, flipped and bonded to the foundation wafer oxide-to-oxide. The top wafer is then "smart cut"—a method borrowed producers of silicon-on-insulator wafers—to form a silicon surface for the rest of the FPGA. Normal wafer processing steps can then fabricate the gate array which is topped by the anti-fuse interconnection layer.

Normal etching steps allow metal connections from the anti-fuses interconnection array to the buried programming transistors in the foundation wafer without damaging its own interconnections, because they were made from high-temperature tungsten.

As a result, Or-Bach claims its 3D FPGAs approach ASICs in density, cost, performance, and power.

NuPGA has also patented its 3-D stacking technique, which it believes holds the promise of simplifying the process of stacking DRAM chips on top of processors.

"Our 3-D IC system has a very low silicon area penalty for TSV [through silicon via] connections," said Or-Bach. "We hope that the industry will adopt it as a more effective use of TSVs for 3D ICs."

Today, TSVs for stacking a DRAM atop a processor must go through the DRAM itself, thereby reducing its density by about five percent. But NuPGAs patented approach runs the TSVs through the bonded oxides connecting the two wafers, thereby sidestepping the density penalty normally incurred by stacking a DRAM atop a processor.

Or-Bach, a past winner of the EE Times Innovator of the Year Award, previously pioneered ASICs at eASIC and later at Chip Express. Last year, Or-Bach applied for a patent with Rice University on a graphite-based memory process for creating reprogrammable memory elements, which NuPGA is now using as anti-fuses for its 3D FPGAs.

NuPGA's anti-fuses start out as an open circuit but can be reprogrammed to create a low-resistance connection when pulsed with a high voltage. By arranging anti-fuses in a separate layer above logic, they could boost the interconnection density of FPGAs to rival ASICs, according to Or-Bach. The only problem is that the high-voltage programming transistors take up so much room that they negate the density boost. NuPGA claims to have solved that problem by burying the programming transistors in a 3-D "foundation" layer beneath the traditional FPGA circuitry.

By building a foundation wafer housing all the bulking programming transistors atop a conventional wafer holding logic and interconnect, a 3D FPGA achieves the density of an ASIC (click on image to enlarge).

"The number one deficiency of anti-fuse FPGAs is the area consumed by the high voltage transistors you need for programming," said Or-Bach, founder, president and CEO of NuPGA. "But by moving these transistors underneath in 3D, the FPGA becomes as dense as an ASIC."

NuPGA's 3-D construction technique first fabricates a foundation wafer containing the high-voltage programming transistors interconnected by high-temperature tungsten metalization and capped with an oxide layer. Then a second blank silicon wafer is capped with oxide, flipped and bonded to the foundation wafer oxide-to-oxide. The top wafer is then "smart cut"—a method borrowed producers of silicon-on-insulator wafers—to form a silicon surface for the rest of the FPGA. Normal wafer processing steps can then fabricate the gate array which is topped by the anti-fuse interconnection layer.

Normal etching steps allow metal connections from the anti-fuses interconnection array to the buried programming transistors in the foundation wafer without damaging its own interconnections, because they were made from high-temperature tungsten.

As a result, Or-Bach claims its 3D FPGAs approach ASICs in density, cost, performance, and power.

NuPGA has also patented its 3-D stacking technique, which it believes holds the promise of simplifying the process of stacking DRAM chips on top of processors.

"Our 3-D IC system has a very low silicon area penalty for TSV [through silicon via] connections," said Or-Bach. "We hope that the industry will adopt it as a more effective use of TSVs for 3D ICs."

Today, TSVs for stacking a DRAM atop a processor must go through the DRAM itself, thereby reducing its density by about five percent. But NuPGAs patented approach runs the TSVs through the bonded oxides connecting the two wafers, thereby sidestepping the density penalty normally incurred by stacking a DRAM atop a processor.

说得貌似很有前途的样子...

这个3D chip究竟是怎么回事?不太懂啊

普通的chip不也是后很多layer叠起来的么?

3D就是把几个die堆起来吧,不只是金属

个人感觉近十年内不会发展起来