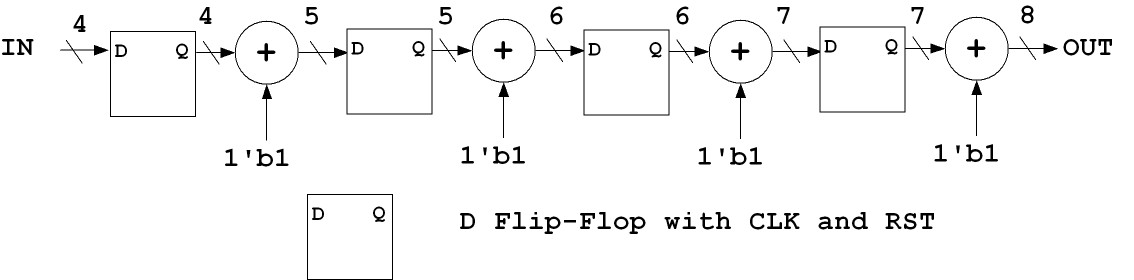

大家看看这个电路能否用Verilog2001的Generate语法生成

要是能用generate生成就省得写脚本了

自顶一个

在Altera的Quartus6.0里面实验能够生成,数据宽度和级数可以通过参数指定

但是有个问题是一开始声明的线网阵列里面有些线网没有用到,让人感到不够

严谨,不过综合器倒是没有报WARNING,是我对标准理解的不够么?

代码如下,附件是Altera Quartus6的RTL View的结果

// module, genshiftaddreg

// author, duweitao@cuc.edu.cn

// date, 2007.May.30th

// usuage, a demo code for generate loop of verilog2K handling loop index

// depended data width

// dscp, a circuit with multi stage, each stage is composed of

// a DFF followed by a adder, the data width of each stage is

// different, we use a wire array 'addOutW' to connect each stage

//

////////////////////////////////////////////////////////////////////////////////

module genshiftaddreg(

RST , // reset

CLK , // clock

IN , // input

OUT ); // output

// change the start and end data width so you can change the

// number of stage

parameter WIDTH_START = 4;

parameter WIDTH_END = 8;

parameter NUMSTAGE = WIDTH_END-WIDTH_START;

input CLK, RST;

input [WIDTH_START-1:0] IN;

output [WIDTH_END -1:0] OUT;

reg [WIDTH_END-1:0] addOutW[NUMSTAGE-1:0];

genvar i ;

generate

for(i = 0; i < NUMSTAGE; i = i + 1) begin : genRegAdd

reg[WIDTH_START+i -1:0] dffR ;

// update the value of DFF

always @ (posedge CLK or posedge RST) begin

if(RST) begin

dffR <= 0;

end // if(RST)

else begin

if(i == 0)

dffR <= IN;

else

dffR <= addOutW[i-1][WIDTH_START+i-1:0];

end // else(RST)

end

// update the value of wire array

always @ (dffR) begin

// the wire array value should be set explicitly

addOutW[i][WIDTH_START+i:0] = dffR[WIDTH_START+i-1:0] + 1'b1;

// the un-used wires in the array(addOutW[i][WIDTH_END-1:WIDTH_END+i+1])

// have no drive in and no drive out signal, so be ignored by the

// synthesizer (verified on Altera Quartus6.0)

end // always(dffR)

end // for(i):genRegAdd

endgenerate

// the output port is assigned to the last stage adder output

assign OUT = addOutW[NUMSTAGE-1][WIDTH_END-1:0];

endmodule // module genshiftaddreg