Verilog基本电路设计之四(去抖滤波)

debounce电路,就是常说的去抖滤波,主要用在芯片的PAD输入信号,或者模拟电路输出给数字电路的信号上。

parameter BIT_NUM = 4 ;

reg [BIT_NUM-1 : 0] signal_deb ; //

always @ (posedge clk or negedge rst_n)

begin

if (rst_n == 1'b0)

signal_deb <= {BIT_NUM{1'b0}} ;

else

signal_deb <= # DLY {signal_deb[BIT_NUM-2:0],signal_i} ;

end

always @ (posedge clk or negedge rst_n)

begin

if (rst_n == 1'b0)

signal_o <= 1'b1 ;

else if (signal_deb[3:1]==3'b111)

signal_o <= # DLY 1'b1 ;

else if (signal_deb[3:1]==3'b000)

signal_o <= # DLY 1'b0 ;

else ;

end

上面的电路,第一个always,还兼顾了去亚稳态作用。它可以滤掉的宽度是两个clk的cycle,对于大于两个cycle而小于三个cycle的信号,有些可以滤掉,有些不能滤掉,这与signal_i相对clk的相位有关。

根据希望滤除的宽度相关,换算到clk下是多少个cycle数,从而决定使用多少级DFF。如果希望滤除的宽度相对cycle数而言较大,可以先在clk下做一个计数器,产生固定间隔的脉冲,再在脉冲信号有效时使用多级DFF去抓signal_i;或者直接将clk分频后再使用。

谢谢分享

我想点个菜,不知小编这里有没有,low power design for front end.

在检测到有效信号后,该电路对非有效信号到来时刻的判断有些苛刻,需要signal_deb[3:1]里的值全相等才行。是否有一个比特不同,即可进行判断。

这个电路,一旦置1,中间出现小于两个cycle的低电平也会滤掉;一旦置0,中间出现小于两个cycle的高电平也会滤掉。这只是一个示例而已,不是说所有滤波都要这样处理,你可以根据自己的应用需求去修改的。

你说的low power design是针对多电压域设计和power gating,还是指从clock gating以及RTL风格这种级别的low power?

刚刚又想了一下,之前考虑不全面,应该根据实际电路的情况来选择不同的判断依据。有的电路在有效信号期间也是可能抖动的。小编说得有道理。

DVFS和power gating偏后端,一般前端的手段实现不了,讲讲前端可以操作的方法,如clock gating, coding style, logic sharing, area/power trade off, etc.

你说的这个问题,想要讲的比较清楚易懂,需要结合文字代码以及时序图之类,还要适合在帖子里讨论。我先整理,看看好不好弄

if(rst_n==1'b0)

signal_o <= 1'b1 ;

初始值一定为1吗

这个是复位值,我写的较为随意。你最好根据你的信号signal_i的默认值来设置signal_deb以及signal_o的复位值,这样才合理。

哦,这样,谢谢。

感谢分享,看了你的几个讲Verilog基本电路设计,深受启发。

谢 谢 分 享

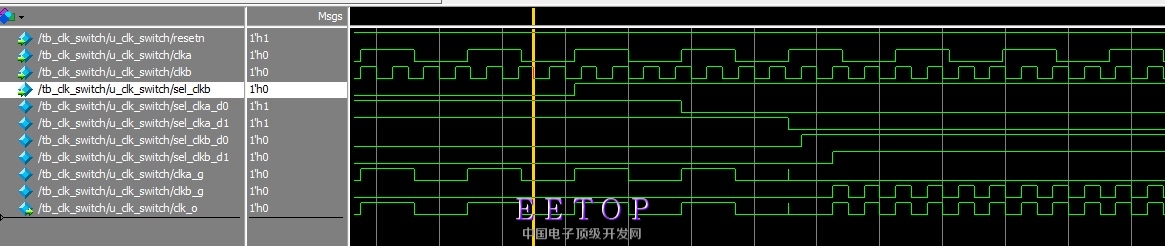

要是有时序仿真图就好了

谢谢指教,我给您发了短信,如果不忙,请指导一下哦,谢谢~!

这个RTL设计可综合吗?

看完4篇文章,受益匪浅,太感谢了

4篇都看完了,受益匪浅,感谢小编。

当然,如果还有干货,小编就别藏着了,赶紧拿出来吧

难道是我的使用方式不对么。我仿真出现一个glitch。

我仿真时,sel_clkb是由clka domain产生的。

另外,我拿掉了part2和part4,相应地,将

sel_clka_d0 <= (~sel_clkb) & (~sel_clkb_dly3) ;

sel_clka_d0 <= (~sel_clkb) & (~sel_clkb_dly3) ;

修改成了

sel_clka_d0 <= (~sel_clkb) & (~sel_clkb_d1) ;

sel_clka_d0 <= (~sel_clkb) & (~sel_clkb_d1) ;

手头上没有gating cell,直接使用的下面这种code:

assign clka_g = clka & sel_clka_d1;

assign clkb_g = clkb & sel_clkb_d1;

assign clk_o = clka_g | clkb_g ;

如果按实际情况分析的话,sel_clkb如果是由clka domain产生,那么sel_clkb相对于clka的rising edge,也应该会有一个小的delay吧(ck to q的delay),那么,clka_g确实会有一个小glitch吧。

召唤小编大大解惑,谢谢。

http://www.eetimes.com/document.asp?doc_id=1202359

又搜到这个网页,感觉里面使用clk falling edge产生select signal的方法挺好。

1、你回复错了帖子,看起来你讨论的是时钟无缝切换。2、你仔细去看看无缝切换那篇,文字描述中第3点说的很清楚,如果你不用gating cell而是用“与”逻辑实现gating,则需要使用到注释掉的下降沿代码

这个应用会比较窄吧

抱歉,回复错帖子了。

又仔细看了看那个帖子,确实是这样,感谢小编。

新手目前也只接触到了按键消抖,小编的文章都看完了,需要时间慢慢消化。希望小编能有新的干货分享给我们!

大佬能对同步复位和异步复位电路做个总结吗?赛灵思好像更推荐同步复位。