有问题吗?

但是log中显示Bitgen Completed Successfully.

所以到底成功没有。

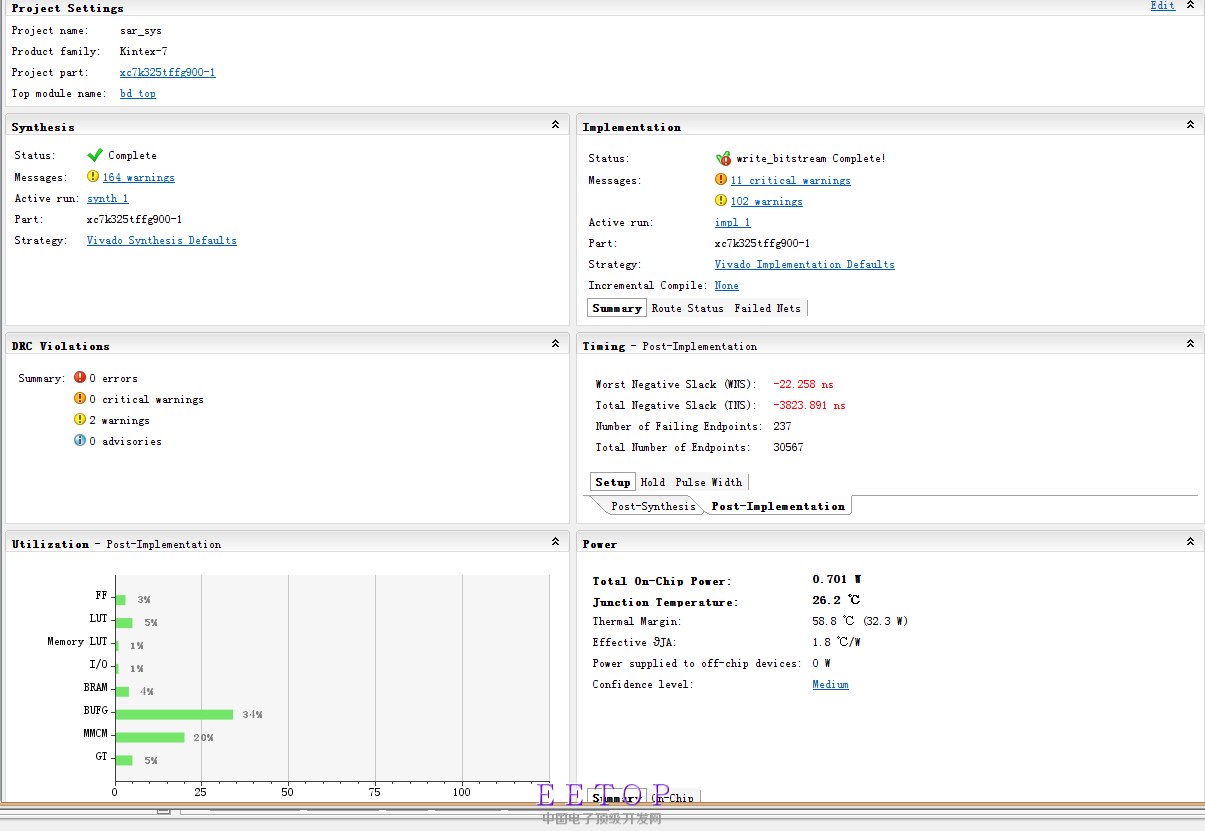

什么有没问题?生成的bitstream,但时序有不满足的路径

我的意思是有时序不满足的时序路径,怎么还能生成bitstream.

在没有进行时序约束的情况下,软件是有个默认的设置。比如时钟频率默认为1000M,但是你实际只有50M,所以时序不满足很正常。万全没有问题。

对主时钟约束之后,主时钟组竟然不满足时序要求,hold slack不满足,我考虑的解决方法是给这个主时钟加一个延时,不知道行不行,时序再看,了解的不多。

保持时间不足,应该是数据加延时吧?

首先感谢您的热心回复。

确实是数据加延迟。

我再向您请教一个问题,我看到一篇论述说建立时间不满足,只能重新设计,保持时间不满足,往往是在布图后修改,您知道这是为什么吗?

还有一个问题,建立时间不满足可怎么办啊?感觉很棘手,这个应该是时钟加延迟了吧。

重新设计吧,把时序不满足的部分优化一下,降低延时就可以了

因为程序不是我设计的,是一个包装的srio,很复杂,我没有看懂,没法重新设计。可以考虑用多时钟周期路径约束吗?我感觉这个多时钟周期约束就是流水线,不会降低工作频率,可是为什么有的文章会说这样约束会降低时钟频率。

一般不会给时钟加延时。一般根据静态时序报告找到最差路径(最长组合逻辑路径),在不破坏逻辑的情况下插入pipeline。

别人给你的你就找他啥。还有事同步还是异步,不同的情况解决办法不同

嗯。我问了,还在等回复。

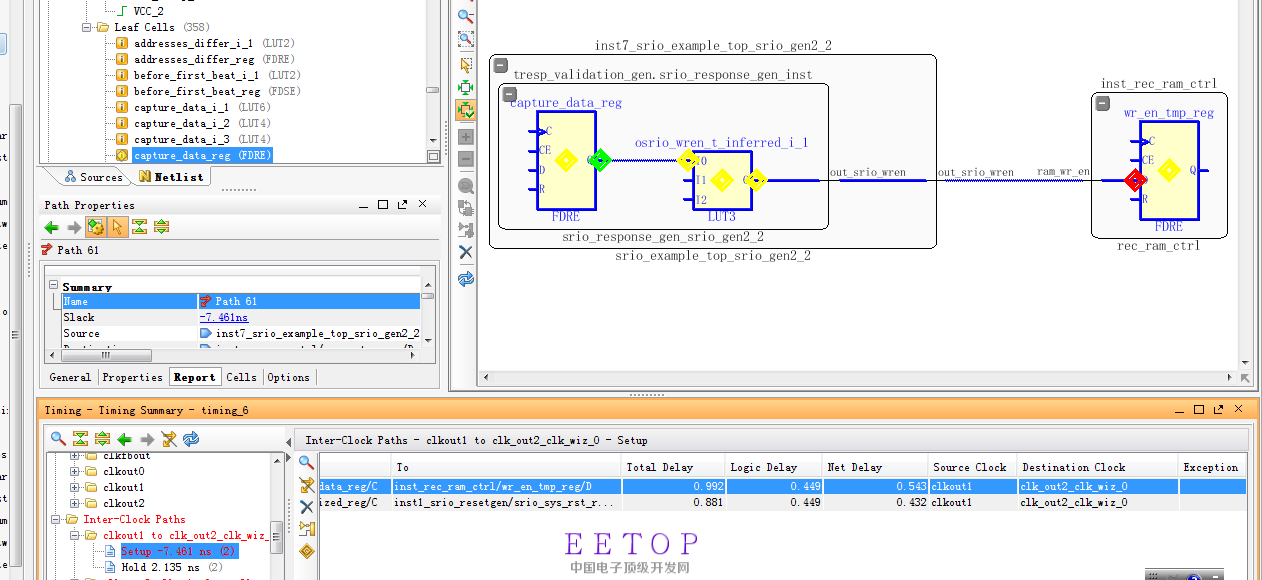

大哥,您是行家,给指导一下吧。源时钟是300M,目的时钟是50M.两个时钟是同步的,由同一个mmcu产生。

建立时间-7.461,图示很清楚。

肯定是要用,set multiple path了, 可是到底应该怎么设置呢。

技术支持不管,说结合你自己的工程,自己添加约束。

帖子更新了,您再看一下。

我按照UG903,瞎试了几次,竟然满足时序了,

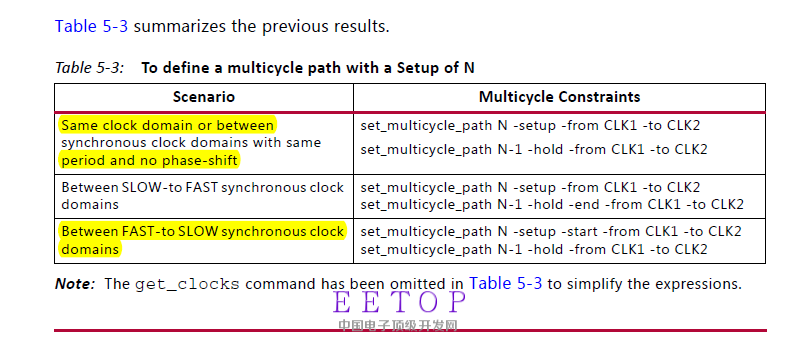

用了两个约束命令:

1:setup 2 from 源时钟 to 目的时钟

2:hold 1 from 源时钟 to 目的时钟

但是我不知道原理是什么,源时钟是目的时钟的6倍,改成setup 6=,hold =5也可以,只不过建立还有保持裕量都很大。

设置成2,1的时候,建立裕量是12.539,保持裕量是7.735.

我不是很清楚原理。

希望您给解答一下。

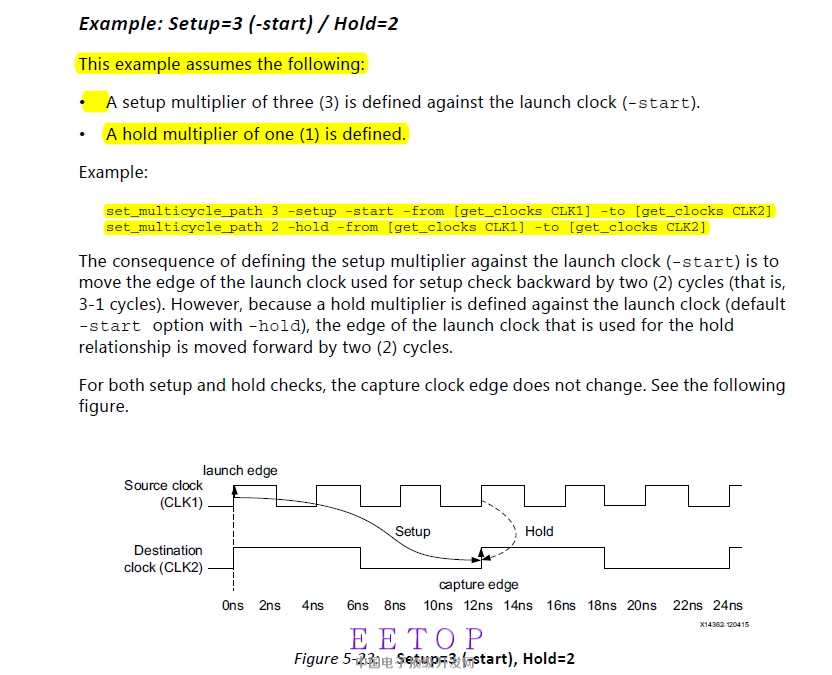

有样比样,是快时钟到慢时钟,应该是按照图示的命令,setup start设置成6,而hold设置成5,建立时间就会满足,但是值很大,120.539

setup start设置成2,而hold设置成1,建立时间也满足,slack是18.139,

我还发现了一点,不管怎样设置,只要setup -start设置等于N,而hold=N-1,则保持时间是不变的=2.135

因此我大胆的猜测,这种设置方法,就是单纯的给建立时间多给周期的裕量,因此设置成2,1就是完全可以的。

具体的原理我不是很懂,我希望您能指点一二。

后面还有好几条路径,也有问题,是慢时钟到快时钟,源时钟50M,目的时钟300M,同步时钟,这里,建立时间裕量倒是满足,知识保持时间不满足了。感觉就是对称着来的。

为何不用异步FIFO或者双端口ram?

用的就是双口RAM.

时序分析部分,我不是很明白,现在快时钟到慢时钟(同步),建立裕量为负,修改时应该是设置成setup -start N,hold N-1;这个我倒是理解。

但是快到慢,保持时间不满足;慢到快,保持时间不满足,我不会设置怎么约束。

双端口ram一般是不需要约束的,时序不满很正常,用一个set_false_path就可以了

你是否有以下情况:

1.花了大量时间自学,学了一大堆,却不知道有没有用?!

2.能看懂别人的代码,到自己设计时却不知道先从哪里下手?!

3.找不到工作,面试难?!看别人有10K+薪水,而自己只有几K?!

不要犹豫了,赶紧来报班培训吧,自学没个几年根本达不到就业水平,时间就是金钱,早掌握早赚钱。

明德扬专业FPGA培训,带你摆脱上面的三种情况,一对一辅导教学,您完全掌握了老师才开始下一个知识点的教学,不用担心大班教学跟不上其他学员进度,明德扬承诺能真正让你拥有独立完成任意FPGA项目的能力。

就业班:10800

周末班:7999

网络班(线上真人教学):5999

20000以下找对手,欢迎对比,了解更多请Q我821219077,竭诚为您服务。