setup/hold的launch和capture都在同一个沿

时间:10-02

整理:3721RD

点击:

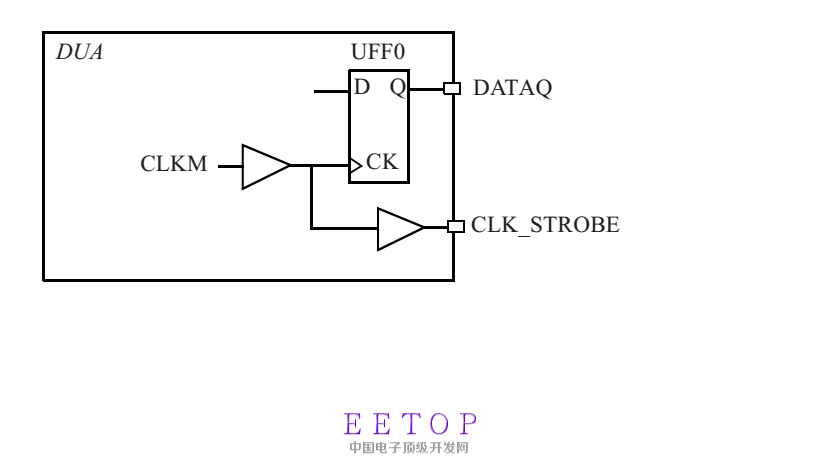

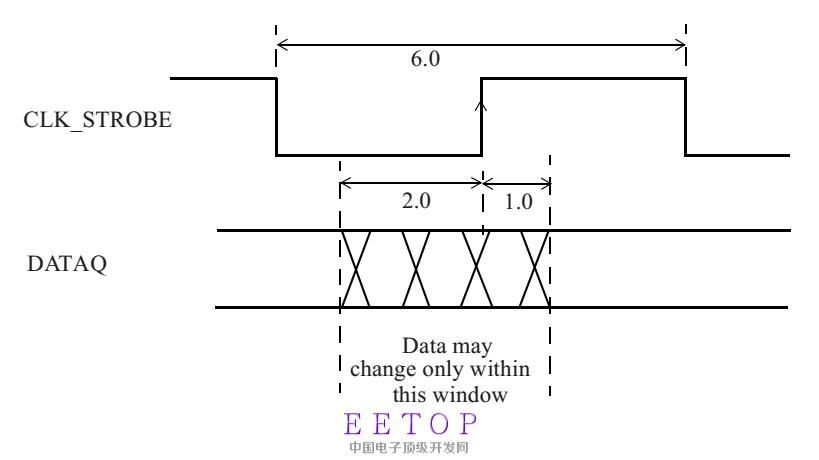

按书上的说法,有这种场景,在时钟沿附近数据才能变,那时钟怎么才采样数据(接受端怎么采数据)?

而且把setup/hold的launch和capture都约束到同一个沿分析

1

1

图片重复了

it did not make sense that requirement. The clock strobe, rising edge would not be able to tell if it catches the change then.感谢有心人。谢谢!

DATAQ不是根据时钟CLK_STROBE来改变的,应该是CLKM反向后的时钟,采样沿不一样

图中的意思就是你设计中时钟下降沿输出的数据要保证时钟的上升沿能采样到, 并且setup slack有2ns。 你只需要设置set_output_delay -min 2 -clock CLK_STORBE 【get_ports DATAQ,关于上升沿采样的hold 的1ns , 你可以不在乎, 因为你是数据是在下降沿输出,上升沿采样的hold是完全足够的