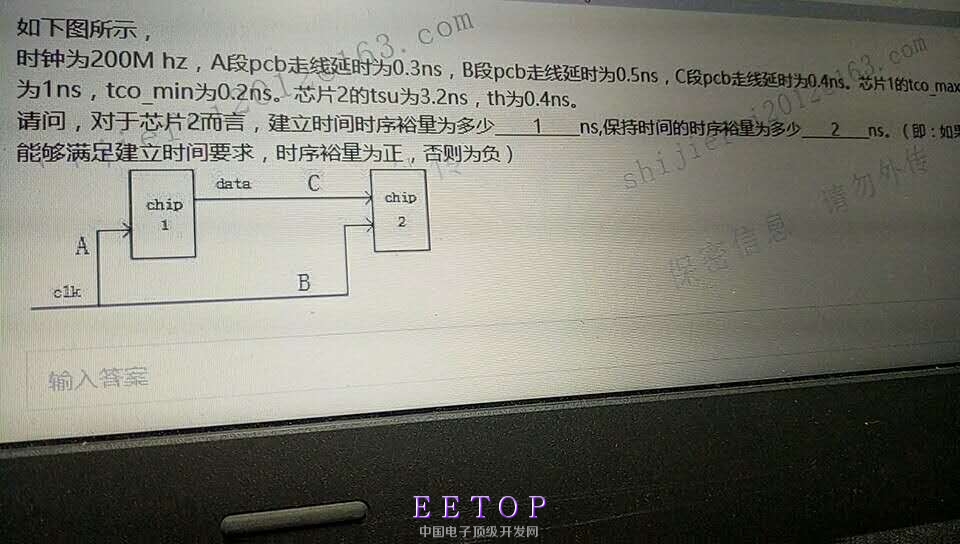

迈瑞笔试,死的惨,有一个问题我难以释怀。

但是关于FPGA的一个问题我却难以释怀。

说说吧,让我好歹有点收获吧,搞清楚这个建立时间,保持时间。先不细说了,我要做下一场笔试。

抢救一下帖子。

谁能给画一下这个时序图,感觉很有用。而且是从什么时候data开始从芯片1往芯片二走。这是很关键的,我不知道他什么时候动作。

唉,大神留步说句话,给个提示也可以。

我希望的是真正的理解,而不是公式的套用。现在我比较忙,静不下心来好好看。

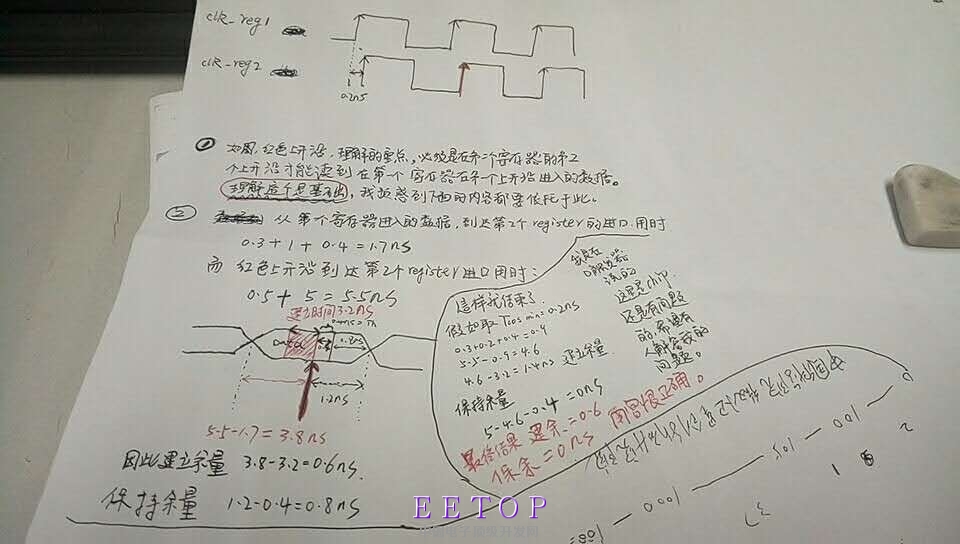

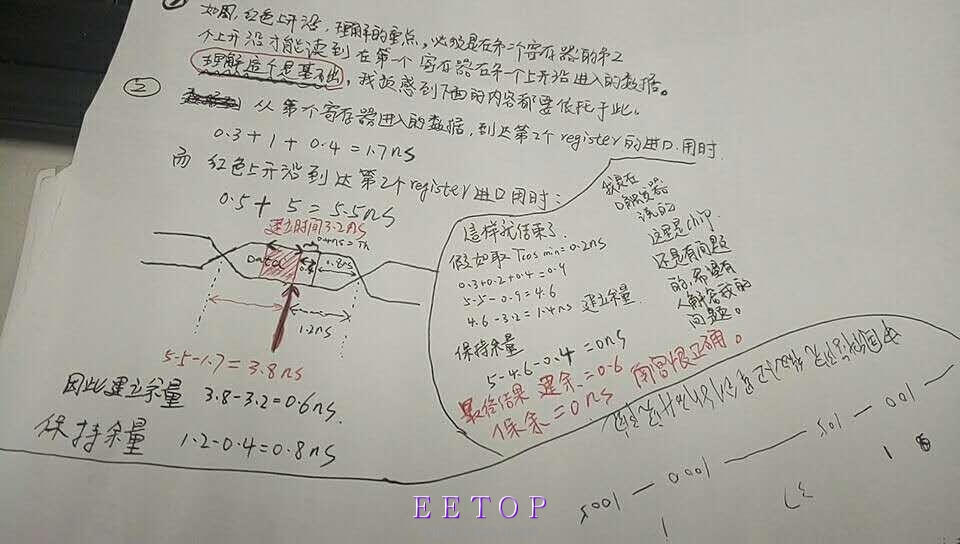

建立时间: 0.3+1+0.4 = 1.7ns

5+0.5 = 5.5ns

5.5-1.7 = 3.8ns (setup slack)

保持时间: 0.3+0.2+0.4 = 0.9ns

0.9-0.5 = 0.4ns (hold slack)

建立时间: 0.3+1+0.4 = 1.7ns

5+0.5 = 5.5ns

5.5-1.7 - 3.2 = 0.6ns (setup slack)

保持时间: 0.3+0.2+0.4 = 0.9ns

0.9-0.5 - 0.4= 0ns (hold slack)

两个大神给的答案非常的神似,但是又有所区别,要是给个解释就好了,不过给了我个思路,我再研究一下。

0.6ns (setup slack)

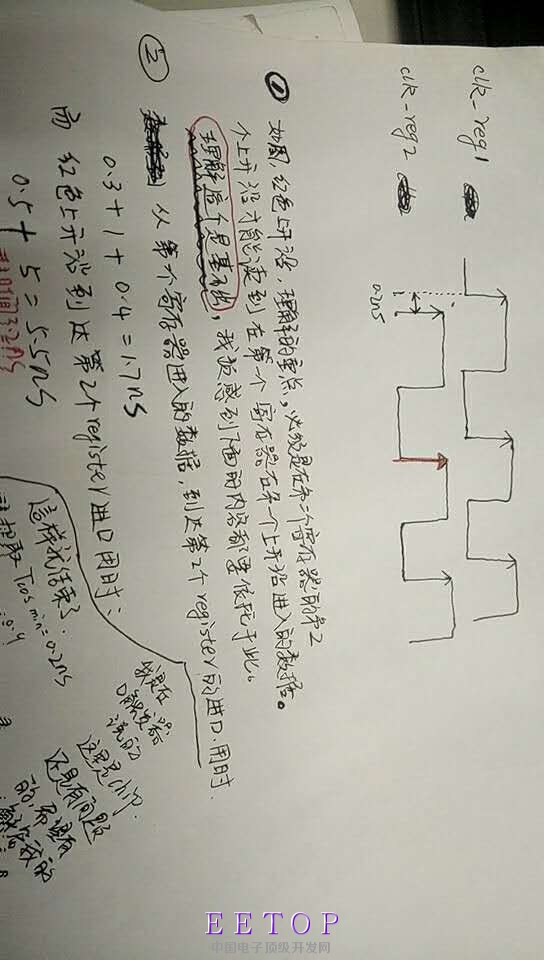

南宫恨是正确的,但是我还是有一些疑问。相信大家看了我的解说,一定会有脱胎换骨的理解,但是还是有些瑕疵,需要大家修补,我的疑问也在截图中有所标示。

大家也已经看出来啦,我是把chip理解成了D触发器做的,实际上也是合理的,因为数据经过芯片用时最大1ns,一个时钟周期就完全可以完成,不会出现好几个时钟周期,数据才能传过去。

堪称完美的解释。关于建立时间,还有保持时间我一共就发两贴,个人认为比那些长篇大论有用的多,而且理解起来也比较直观,容易,相当于一个很基础的教学,我总认为,知识看起来很复杂,很可能是表达的方式不对,或者说故作高深。

南宫很是完全正确的。

因为tco有两个值,一个最大值,一个最小值 。因此会算出来两组值。

取最大值时,建余0.6ns,保余0.8ns.

取最小值时,建余1.4ns,保余0ns.

因此最终取每组的最小值,建余0.6ns,保余0ns.

我觉得就是这样。

公式:setup slack=T+Tpd—Tsetup-Tdelay-Tcomax=0.6ns;

hold slack=Tcomin+Tdelay-Tpd-Thold=0ns;

这个公式,打死我,我都不会记住。记公式不是那么简单,要死人的。

要清楚概念,不要记公式,建立时间是说时钟有效沿,需要采样的数据需要保持稳定的时间,在这里是tsu=3.2ns,那么需要采样的数据需要在时钟有效沿之前的3.2ns就已经稳定了,需要采样的数据是前面某寄存器在上一个沿输出的,那么考虑时钟tco tlogic tline等等,计算传输时间,然后将两个时钟沿的差值,减掉传输时间,就是数据稳定时间,减掉tsu就是余量。

保持时间是说采样后数据仍然需要稳定的时间,对于采样沿,前面的寄存器输出变化,那么这个变化需要在保持时间之后传到这个寄存器,同样是计算传输时间,减去需要的保持时间th,就是余量。

从概念上就能看出来,对于建立时间,延迟越大,传输时间越大,稳定时间越小,所以要用tmax计算建立时间余量。延时越小,传输时间越小,所以保持时间要用tmin

谢谢您的回复,记公式迟早要忘记,忘记是小事,但是可怕的是对概念没有深刻的认识,掌握并深刻理解基础概念往往有出奇制胜的效果。实际上理解两个关键点,这道题目就会迎刃而解。